Semiconductors

Book S14

1988

Liquid Crystal Displays and Driver ICs for LCD

# Liquid crystal display

# Contents

|                                      |     |     |    |     |     | $p_i$ | age |

|--------------------------------------|-----|-----|----|-----|-----|-------|-----|

| Preface                              |     |     |    |     |     |       | 3   |

|                                      |     |     |    | •   | • • | •     | •   |

| Selection Guide                      |     |     |    |     |     |       | 5   |

| Index                                |     |     |    |     |     |       | 7   |

| Optical selection guide              |     |     |    |     |     |       | 9   |

|                                      |     |     |    |     |     |       |     |

| User Guide                           | ٠.  |     |    |     |     |       | 17  |

| Introduction                         |     | ٠.  |    |     |     |       | 19  |

| Structure of an LCD                  |     |     |    |     |     |       | 19  |

| The LCD in operation                 |     |     |    |     |     |       | 20  |

| Illumination modes                   |     |     |    |     |     |       | 21  |

| Colour in TN LCDs                    |     |     |    |     |     |       | 21  |

| Optical properties                   |     |     |    |     |     |       | 21  |

| Driving LCDs                         |     |     |    |     |     |       | 22  |

| Electro-optical characteristics      |     |     |    |     |     |       | 25  |

| Derived technologies                 |     |     |    |     | •   | Ī     | 26  |

| Connecting techniques                | • • | • • | •  | • • | • • | •     | 27  |

| Mounting and illumination techniques |     |     |    |     | •   |       | 29  |

| 4                                    |     | •   | •  | • • | • • | •     |     |

| LCD modules                          |     |     |    |     |     |       | 31  |

| Introduction to LCD modules.         |     |     |    |     |     |       | 33  |

| Segment display modules              |     |     |    |     |     |       | 33  |

| Character display modules            |     |     |    |     |     |       | 34  |

| Dot matrix display modules           |     |     |    |     |     |       | 34  |

| Dot matrix display modulos           |     | • • | •  | • • | • • | •     | 54  |

| 0                                    |     |     |    |     |     |       | •   |

| Quality                              | • • |     | ٠. | ٠.  | • • | •     | 39  |

|                                      |     |     |    |     |     |       |     |

| Custom Design                        |     |     |    |     |     |       | 45  |

| Introduction to custom design        |     |     |    |     |     |       | 47  |

| Development procedure                |     |     |    |     |     |       | 47  |

| Semi-standard products               |     |     |    |     |     |       | 47  |

| Custom products                      |     | ٠.  | •  | ٠.  | • • | •     | 53  |

|                                      |     |     |    |     |     |       |     |

| Type Code Information                |     |     |    |     |     |       | 55  |

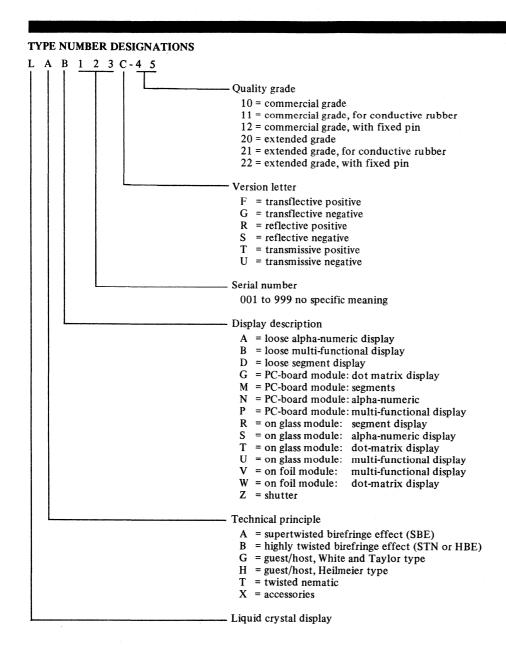

| Type number designations             |     |     |    |     |     |       | 57  |

| Cross reference guide                |     |     |    |     |     |       | 58  |

|                                      |     |     |    |     |     |       |     |

| General LCD Family Characteristics   |     |     |    |     |     |       | 59  |

|                                      |     |     |    |     |     |       |     |

| LCD cell data                        |     |     |    |     |     |       | 71  |

|                                      |     |     |    |     |     |       |     |

| LCD Module Data                      |     |     |    |     |     | . 1   | 87  |

|                                      |     |     |    |     |     |       |     |

| Driver ICs for LCD                   |     |     |    |     |     |       |     |

| Dedicated LCD drivers                |     |     |    |     |     | . 2   | 45  |

| Peripheral LCD drivers               |     |     |    |     |     | 4     | 35  |

## Preface

#### PREFACE

cated devices.

This data handbook incorporates information about LCD cells, LCD modules and driver ICs for LCD. LCD cells are versatile displays with a large number of superior features. These include low power consumption, high legibility (even in bright sunlight), thin outline and flexibility in pattern design, making them very suitable for customization.

Modules are the incorporation of LCD cells and IC drivers into one unit. The thin outline of the cells enable the module to remain compact and easy to mount in a variety of applications. We offer both full-dot graphic and character display modules in twisted nematic (TN) liquid crystal technology (see the chapter "User guide").

With the advent of supertwisted nematic (STN) technology, the application areas of LCD have expanded enormously. STN creates the possibility of high information density displays with far better viewing angles and contrast than TN displays (see the section Derived technologies of the chapter "User guide"). Driver ICs for LCD can be both dedicated and non-dedicated microcontrollers or microprocessors. Full data is included in this handbook for the dedicated devices and brief data is included for the non-dedi-

As LCDs can be custom designed the handbook contains a custom design section and a pull out order form for completion by the prospective customer.

For more information on the principles of LCD refer to the chapter "User guide". Standard cell data is contained in the chapter "LCD data" and module data for twisted nematic modules is contained in the chapter "LCD module data". Data for driver ICs is contained in the chapter "Driver ICs for LCD".

# Liquid crystal display

# Selection guide

|                         | page |

|-------------------------|------|

|                         |      |

| Index                   | 7    |

|                         | ,    |

| Optical selection guide | 9    |

|                         |      |

on the figure, the part of

# Index

### Index

### LCD cells

| BASIC TYPE NUMBER | DESCRIPTION  | DRIVE* | DIMENSIO | PAGE   |           |

|-------------------|--------------|--------|----------|--------|-----------|

|                   |              |        | WIDTH    | HEIGHT |           |

| LP-2703-B         | 3½-digit     | 1:2    | 38.6     | 20.8   | 75        |

| Е1-2703-В         | clock LCD    | 1.2    | 36.0     | 20.8   | /3        |

| LTA141            | 5 x 7 dot    | DD     | 50.8     | 80.0   | 79        |

| E171141           | matrix       | l DD   | 30.0     | 00.0   | 1 19      |

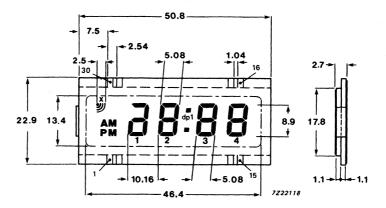

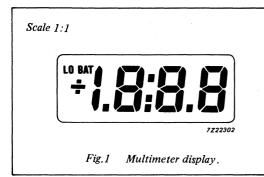

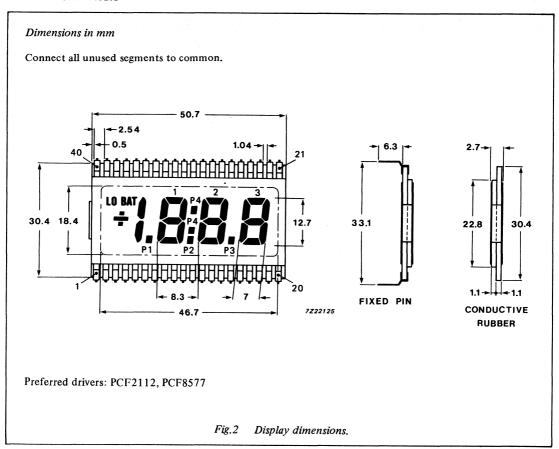

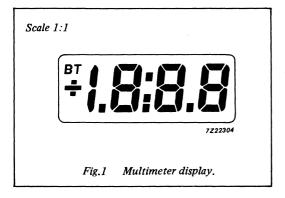

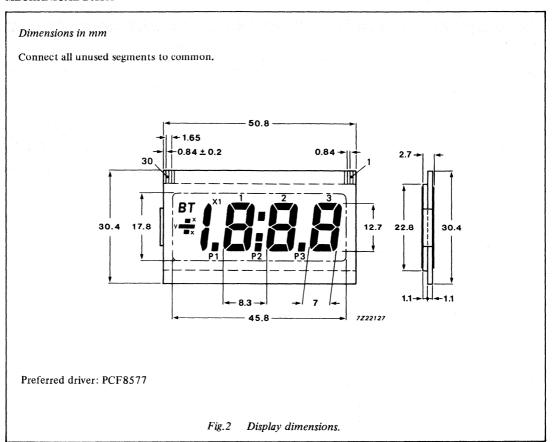

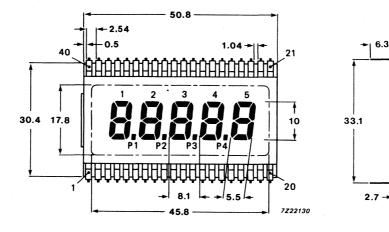

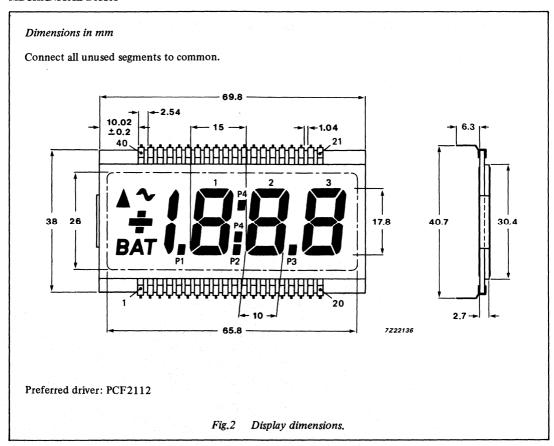

| LTD101            | 3½-digit     | DD     | 50.8     | 22.9   | 83        |

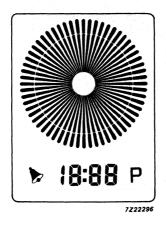

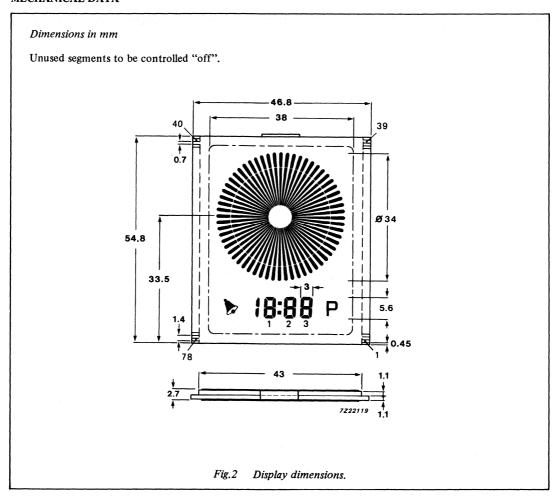

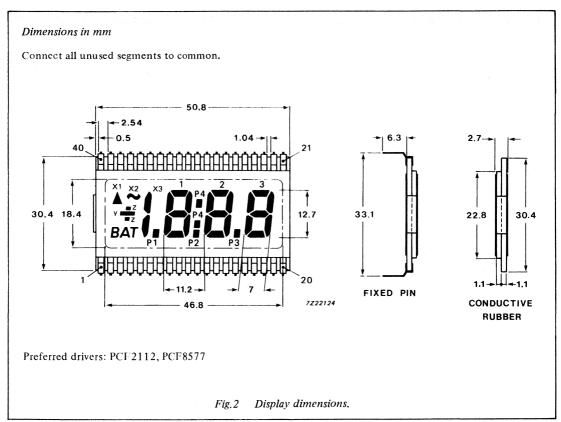

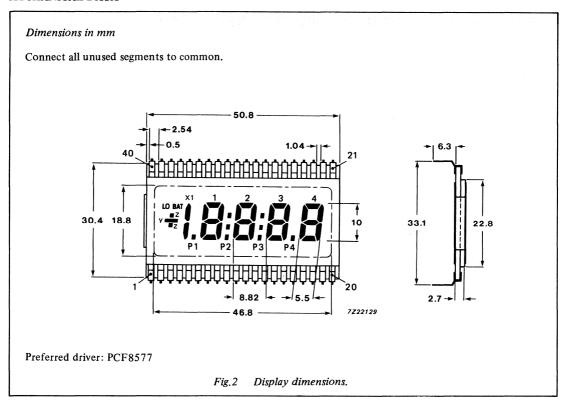

| LTD132            | 3½-digit     | 1:2    | 46.8     | 54.8   | 87        |

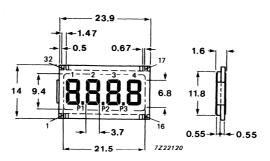

| LTD201            | 4-digit      | DD     | 23.9     | 14.0   | 91        |

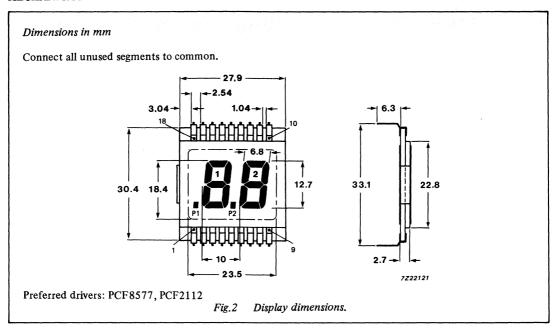

| LTD202            | 2-digit      | DD     | 27.9     | 30.4   | 93        |

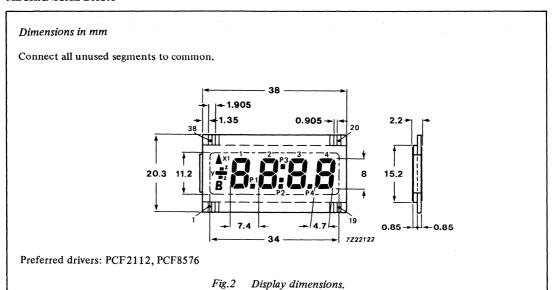

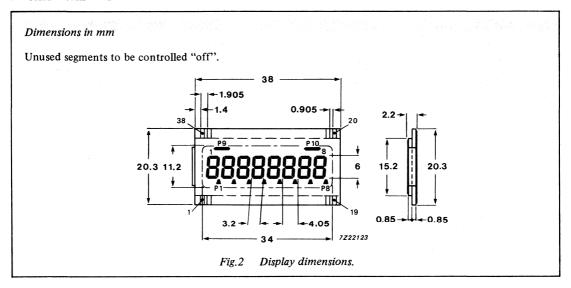

| LTD203            | 4-digit      | DD     | 38.0     | 20.3   | 95        |

| LTD211            | 8-digit      | 1:2    | 38.0     | 20.3   |           |

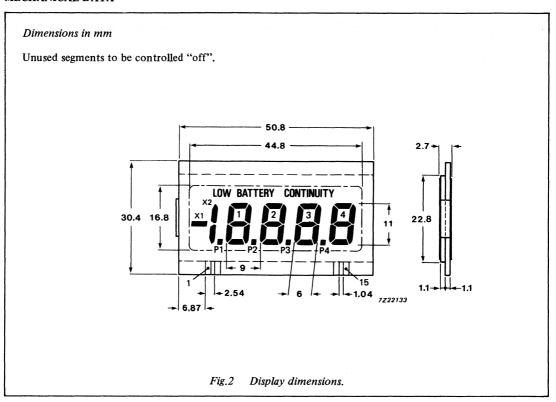

| LTD221            | 3½-digit     | DD     | 50.8     | 30.4   | 99<br>103 |

| LTD222            | 3½-digit     | DD     | 50.8     | 30.4   | 103       |

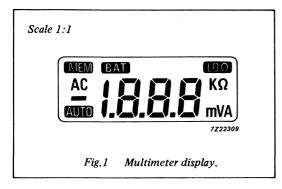

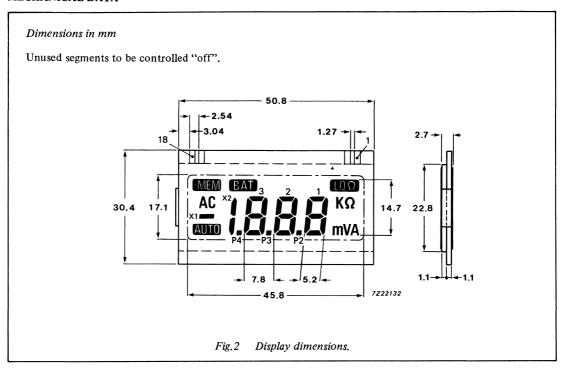

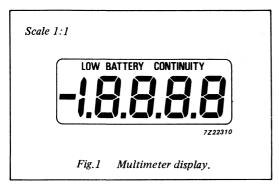

|                   | multimeter   | DD     | 30.6     | 30.4   | 107       |

| LTD224            | 3½-digit     | DD     | 50.8     | 30.4   | 111       |

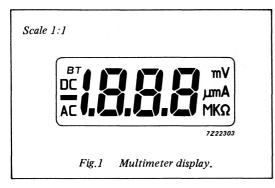

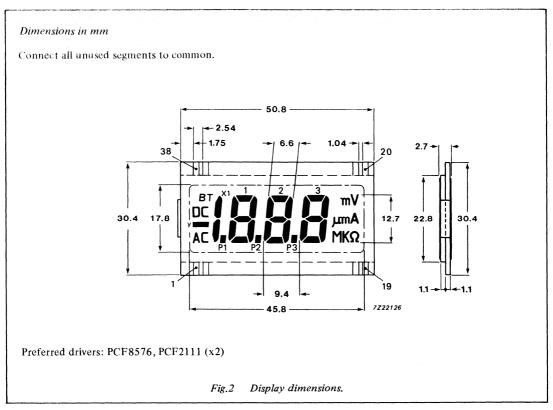

| 272221            | multimeter   | DD     | 30.0     | 30.4   |           |

| LTD225            | 3½-digit     | DD     | 50.8     | 30.4   | 115       |

| 21222             | multimeter   | DD     | 30.0     | 30.4   | 113       |

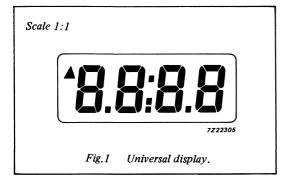

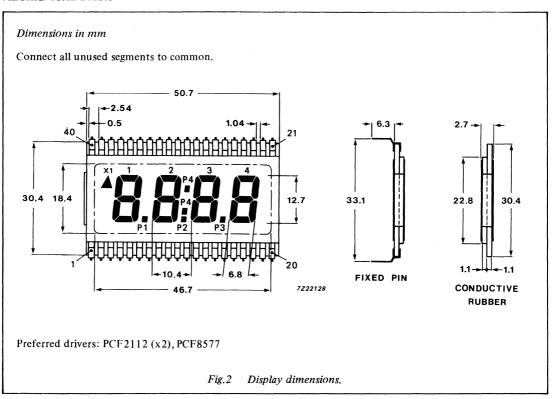

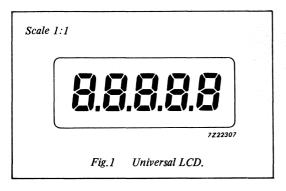

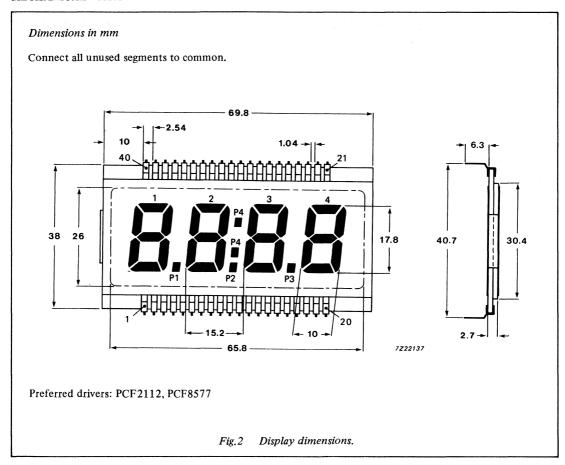

| LTD226            | 4-digit      | DD     | 50.8     | 30.4   | 119       |

| LTD227            | 4½-digit     | DD     | 50.8     | 30.4   | 123       |

|                   | multimeter   | l DD   | 30.0     | 30.4   | 123       |

| LTD228            | 5-digit      | DD     | 50.8     | 30.4   | 127       |

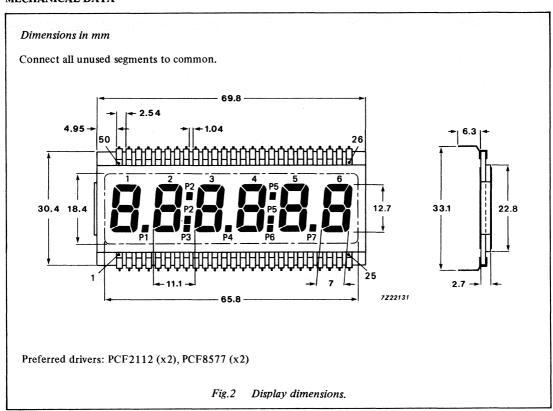

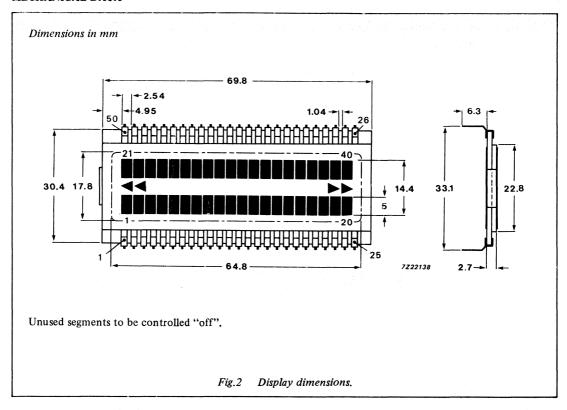

| LTD229            | 6-digit      | DD     | 69.8     | 30.4   | 131       |

| LTD231            | 3½-digit     | 1:3    | 50.8     | 30.4   | 135       |

| 212231            | multimeter   | 1.5    | 30.0     | 30.4   | 133       |

| LTD232            | 4½-digit     | 1:3    | 50.8     | 30.4   | 139       |

| 212232            | multimeter   | 1.5    |          |        | 139       |

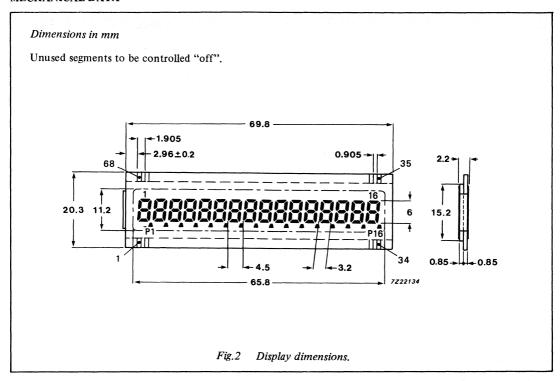

| LTD233            | 16-digit     | 1:2    | 69.8     | 20.3   | 143       |

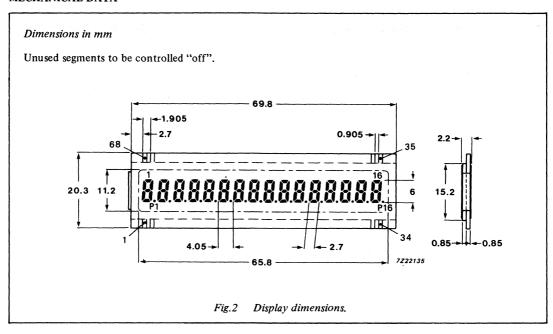

| LTD234            | 16-digit     | 1:4    | 69.8     | 20.3   | 147       |

| LTD241            | 3½-digit     | DD     | 69.8     | 38.0   | 151       |

|                   | multimeter   |        | 07.0     | 30.0   | 131       |

| LTD242            | 4-digit      | DD     | 69.8     | 38.0   | 155       |

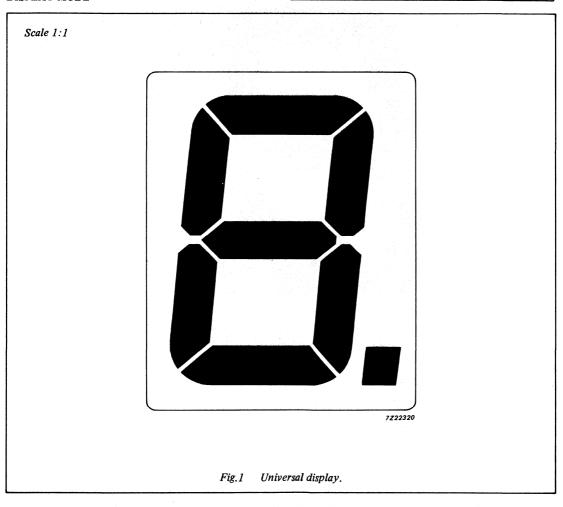

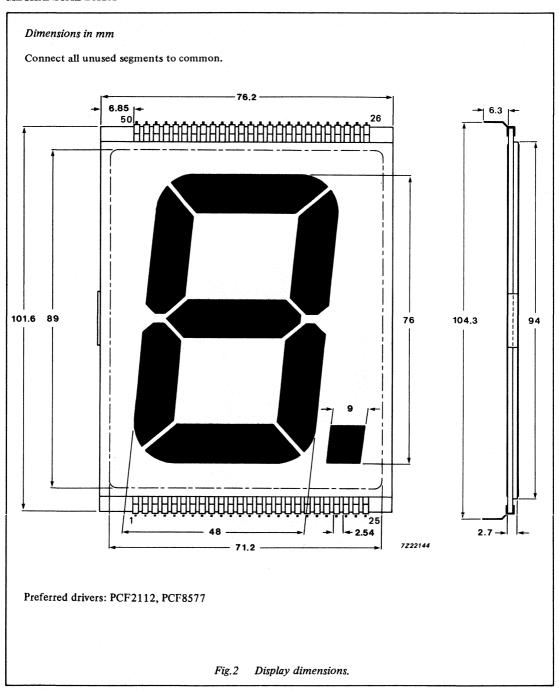

| LTD261            | 1-digit      | DD     | 76.2     | 101.6  | 159       |

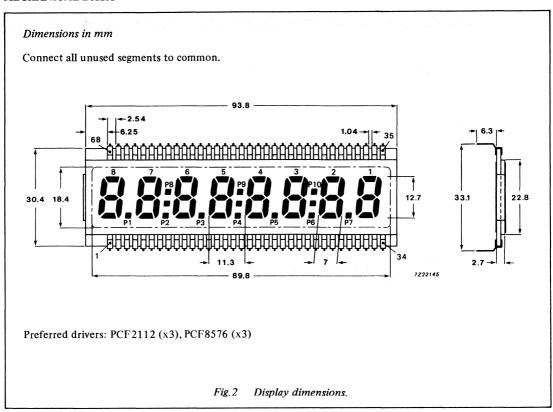

| LTD262            | 8-digit      | DD     | 93.8     | 30.8   | 163       |

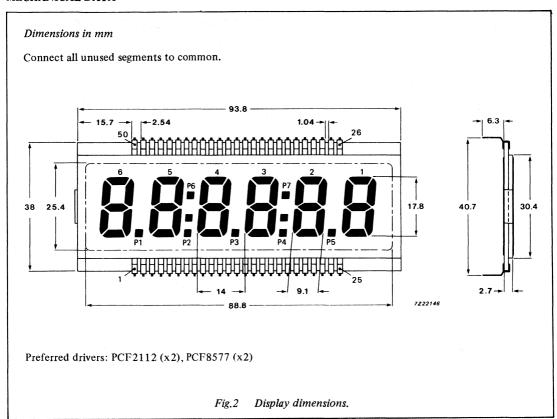

| LTD263            | 6-digit      | DD     | 93.8     | 30.8   | 167       |

| LTD264            | 5-digit      | DD     | 114.0    | 26.0   | 171       |

| LTD321            | bargraph     | DD     | 69.8     | 30.4   | 175       |

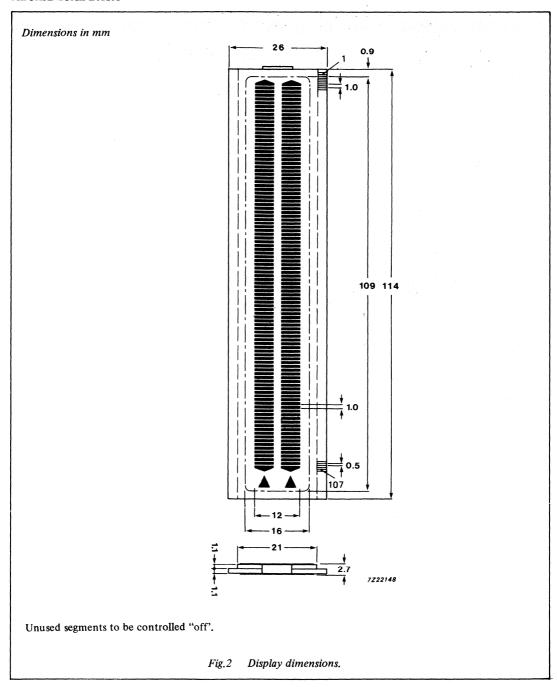

| LTD351            | bargraph     | 1:2    | 26.0     | 114.0  | 179       |

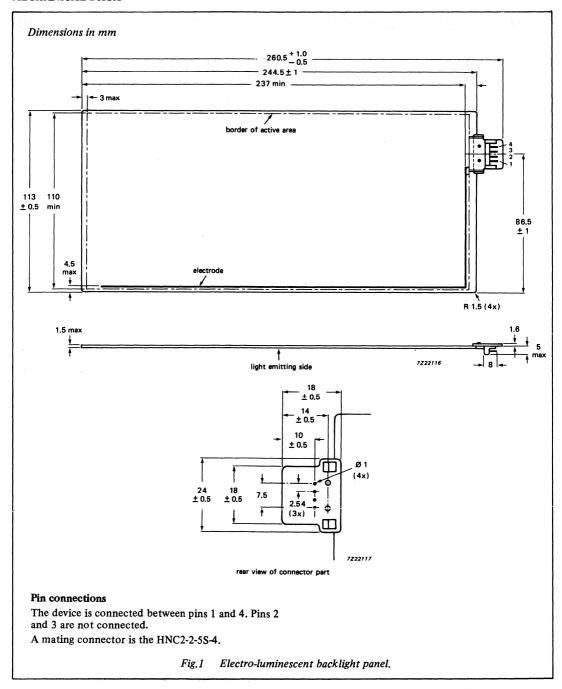

| LXL401-W          | EL backlight | 1.2    | 20.0     | 114.0  | 183       |

<sup>\*</sup> DD = direct drive

Index (cont.)

## LCD modules

| BASIC TYPE NUMBER | DESCRIPTION                   | DRIVE | DIMENSIO | PAGE   |     |

|-------------------|-------------------------------|-------|----------|--------|-----|

|                   |                               |       | WIDTH    | HEIGHT |     |

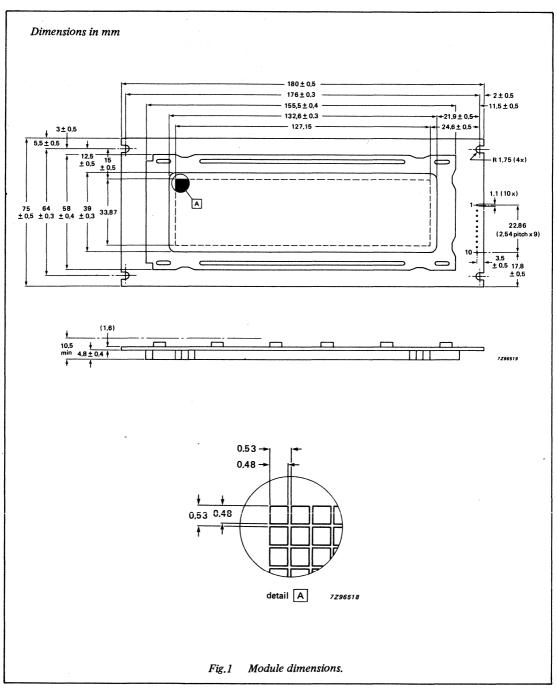

| LTG201            | graphic<br>full dot<br>module | 1:64  | 180.0    | 75.0   | 189 |

| LTG401            | graphic<br>full dot<br>module | 1:100 | 256.0    | 125.0  | 197 |

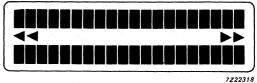

| LTM233            | 16-digit<br>module            | 1:2   | 92.5     | 25.0   | 207 |

| LTN111            | dot matrix<br>module          | 1:16  | 80.0     | 36.0   | 213 |

| LTN211            | dot matrix<br>module          | 1:16  | 84.0     | 44.0   | 223 |

| LTN241            | dot matrix<br>module          | 1:16  | 182.0    | 33.5   | 233 |

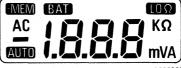

LTD203

LTD211

LTD101

LP-2703

LTD202

LTD233

LTD234

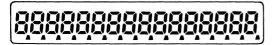

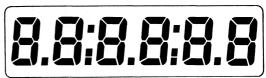

8.8.8.8.8.8.8.8.8.8.8.8.8.8.8.

7Z2231

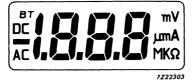

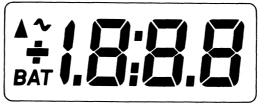

LTD222

LTD224

LTD225

7222307

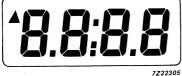

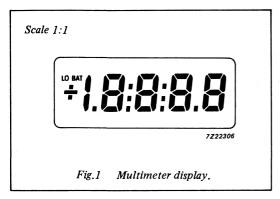

**LTD227**

7Z22306

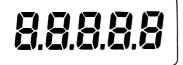

**LTD228**

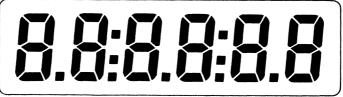

LTD231

**LTD232**

LTD229

7Z2231

LTD241

7222313

**LTD242**

7222314

LTD263

7222316

7222317

## LTD264

## LTD261

LTD321

/22231

## LTD351

7Z22319

## LTA141

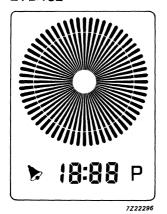

## LTM233

### LTN111

## LTN211

## LTN241

7222325

# Liquid crystal display

# User guide

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |   | <br> |     |   |     |     |   |    | _ | -   |   |   |   |   |     | _ |     |   |   |     | - |   | -   |   |   |     |   | _   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---|------|-----|---|-----|-----|---|----|---|-----|---|---|---|---|-----|---|-----|---|---|-----|---|---|-----|---|---|-----|---|-----|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |   |      |     |   |     |     |   |    |   |     |   |   |   |   |     |   |     |   |   |     |   |   |     |   |   |     | p | age |

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |   |      |     |   |     |     |   |    |   |     |   |   |   |   |     |   |     |   |   |     | • |   |     |   |   |     |   | 19  |

| C TOD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |   |      |     |   |     |     |   |    |   |     |   |   |   |   |     |   |     | • |   |     | • |   |     | • | • | • • | • |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |   |      |     |   |     |     |   |    |   |     |   |   |   |   |     | • |     | • | • | • • | • | • | • • | • |   |     | - |     |

| was                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |   |      |     |   |     |     |   |    |   |     |   |   |   |   |     | • |     | • | • |     | • | • | • • | • | • |     | - |     |

| Colour in TN LCDs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |   | <br> |     |   |     | ٠.  | • | ٠. | ٠ | • • | • |   | • | • | • • | • | • • | • | • | • • | • |   | • • | • | • | •   |   | 21  |

| Optical properties Driving LCDs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |   | <br> | • • | • | • • | • • | • |    | • | • • | • | • | • |   |     | • |     | • |   |     |   |   |     |   |   |     |   | 2   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _        |   |      |     |   |     |     |   |    |   |     |   |   |   |   |     |   |     |   | • |     | • | • |     |   | • |     |   |     |

| The state of the s |          |   |      |     |   |     |     |   |    |   |     |   |   |   | • |     | • |     | • | • |     | • | • | ٠,  |   | • |     |   | _   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |   |      |     |   |     |     |   |    |   |     |   |   |   |   |     | • |     | • | • |     | • | • |     |   | • |     |   |     |

| Connecting techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | echnique | s | <br> |     |   |     |     |   |    |   |     |   |   |   | ٠ |     | • | ٠.  | • | • | ٠.  | • | • | •   |   | • | • • |   |     |

#### INTRODUCTION

Liquid crystals are materials which combine the properties of both liquids and crystals. Rather than a melting point they have a temperature range, known as a mesophase, within which the molecules are almost as mobile as they would be in a liquid, but are grouped together in an ordered form similar to that of a solid crystal.

Around 1970 it was found that thin layers of a certain type of liquid crystal can be switched from transparent to opaque or vice-versa, by application of a voltage. This property is the fundamental operating principle of all Liquid Crystal Displays (LCDs).

The main advantages and features of LCDs are:

- Flat and compact size: LCDs are lightweight and very thin; the thickness of the display is only a few millimeters

- Low power consumption: low power and supply voltage requirements mean that they can easily be powered over long periods by batteries and at the same time be compatible with modern electronic circuits e.g. CMOS

- Passive display: LCDs do not generate light and as such are comparable to printed material. One needs light to read the display and it does not fade as the ambient light increases. Reading in dark conditions is possible with the use of back lighting

- Reliable: LCDs have a wide operating temperature range and a long life

- Flexible design: a change in display size or layout is relatively simple, making LCDs very suitable for customization

- Low cost: LCDs are the most economically produced flat display system, including drive and supply aspects

Initially LCDs were used almost exclusively in watches, calculators and measuring instruments. These were simple, usually seven segment displays with a limited amount of numeric data. More recent advances in technology have extended legibility, information content and the temperature range, which has lead to applications in telecommunications, cars, entertainment electronics and computers.

LCDs are now the fastest growing display technology. They are currently replacing the CRT for the display of text and graphics and may eventually replace the CRT in TV applications.

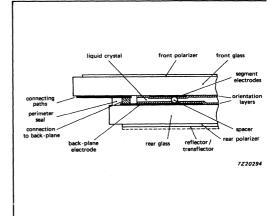

#### STRUCTURE OF AN LCD

An LCD consists of two glass plates which are sealed together with a gap between them of 6 to  $10~\mu m$  (Fig.1). The inner surfaces of the glass plates are coated with transparent electrodes which define the characters, symbols, or other patterns to be displayed The electrode material is usually Indium/Tin Oxide (ITO)

Between the electrodes and the liquid crystal there are polymeric layers which are treated in a way that induces the adjacent liquid crystal molecules to maintain a defined orientation angle. For this reason, the polymeric layers are also know as the orientation or alignment layers.

The distance between the two plates is set within narrow limits by means of glass fibre spacers or minut plastic balls.

Fig.1 Construction of a liquid crystal display.

#### Liquid crystal

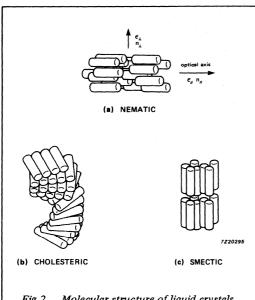

The most common type of liquid crystal used in displays is nematic (Fig.2(a)). In nematic liquid crystal the long rod-like molecules align themselves spontaneously parallel to each other which gives the material anisotropic optical and electrical properties, i.e. it has different properties in different directions. Other classes of liquid crystal which are increasing in significance for displays are cholesteric (Fig.2(b)) and smectic (Fig.2(c)).

Fig. 2 Molecular structure of liquid crystals (a) nematic (b) cholesteric (c) smectic.

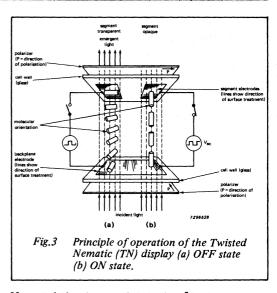

#### THE TN LCD IN OPERATION

The operating principle of Twisted Nematic (TN) LCDs is illustrated in Fig.3. The nematic liquid crystal molecules are anchored in a fixed direction at the top and bottom plates by the orientation layer. As the orientation directions of the top and bottom plates differ by an angle of 90° the crystal molecules are twisted through a 90° helix between the two plates. Polarizing filters are aligned with the orientation directions at the respective sides. Polarized light from the bottom polarizer is then guided by the crystal molecules through the helix to the top plate with its polarization direction rotated by 90°. This property is caused by the optical anisotropy of the molecules. As such the polarization direction is aligned with the top polarizer and the light passes unhindered through it to give the display a bright appearance (Fig. 3(a)). If sufficient voltage is applied across the electrodes the electrical anisotropy of the molecules will cause them to align with the electric field and the 90° twist in the optic axis will be distorted. The light will then pass through the liquid crystal but will maintain its polarization direction and will be absorbed by the second polarizer (Fig.3(b)). On switching off the initial state is restored and the cell is again transparent. Under these conditions the display will appear black when ON and bright when OFF which is known as a positive image display.

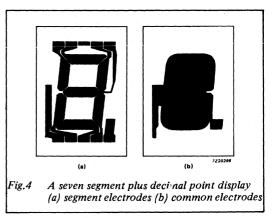

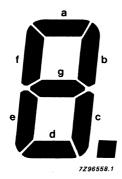

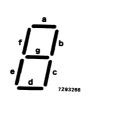

If one polarizer is rotated through 90° the effect will be reversed and the display will appear black under no voltage field conditions and bright when a voltage is applied which is known as a negative image display. When the electrodes completely cover the top and bottom plates the LCD will act as a light shutter. A more usual arrangement is for the electrodes to be patterned such that specific segments can be switched to form numbers, letters, or graphics. An example of this is the basic seven segment digit shown in Fig.4. Any number can be displayed by switching on the appropriate electrodes that form the various segments. It should be noted that segments are only formed where the segment electrodes and the common (backplane) electrode overlap; the remaining parts of the electrodes are required for connections to the outside.

#### **ILLUMINATION MODES**

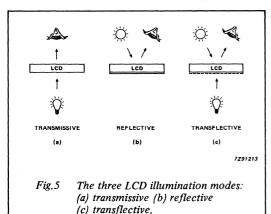

LCDs can be operated in one of three modes, depending on the ambient light conditions:

- Reflective mode: where the LCD is backed by a

diffuse metallic reflector, such as brushed aluminium foil, that reflects ambient light back through

the display. This mode is best suited to applications

where there is always sufficient ambient light.

Reflective mode is especially suited to battery

operated displays as no lighting power is required

(Fig.5(b)).

- Transmissive mode: where the display is lit from behind. Negative image displays are best suited to this mode. Their appearance is similar to active displays such as Light Emitting Diodes (LEDs), Vacuum Fluorescent Displays (VFDs) etc. This type of display can be projected like a slide (Fig.5(a)).

- Transflective mode: is a combination of transmissive and reflective modes. The display is backed by a partly transmissive reflector (transflector) which reflects ambient light as well as transmitting diffused back-lighting for night use (Fig.5(c)).

#### COLOUR IN TN LCDs

Colour can be introduced into a TN display in three ways: colour selective polarizers, coloured filters and coloured back-lighting.

Colour selective polarizers produce coloured segments on a bright background or bright segments on a coloured background. By using two colour selective polarizers a two colour combination can be produced, for example red and green polarizers will give red segments on a green background or vice versa. Coloured filters may be either foil behind the display or translucent colours printed onto the display itself. They are best suited to transmissive mode LCDs with a negative image i.e. coloured segments on a dark background.

Coloured back-lighting produces black segments on a coloured background or coloured segments on a dark background. It is possible to change the colour of the display by using two different coloured backlights e.g. between red and green, and by using both lights, white. It should be noted that the colour effect in a transflective display will be greatly reduced under high ambient light conditions.

#### **OPTICAL PROPERTIES**

#### Contrast and brightness

The legibility of an LCD depends on a variety of factors such as pattern layout, technology, driving and illumination conditions, viewing direction, viewing angle, viewing distance and operating temperature. The most important optical characteristics that define legibility are brightness and contrast ratio.

The brightness of an LCD is expressed as the luminance of the reflected or transmitted light compared to the luminance of the incident light. For a reflective LCD an MgO surface is used as a reference for testing luminance. The brightness of a TN LCD cannot be higher than 50%, since an ideal polarizer only transmits half the incident light. A reflective display will, therefore, tend to appear rather grey. A brighter display can be obtained by using backlighting.

The contrast ratio  $(C_R)$  of an LCD is the ratio between the brightness of the light areas  $(B_1)$  and the brightness of the dark areas  $(B_d)$  of the display.

i.e.

$$C_R = B_1/B_d$$

For a TN display the typical maximum contrast ratio can range from between 5 and 50.

In a reflective display, the maximum contrast ratio that can be detected by the human eye is normally about 10 and the lower limit of good legibility, about 2. For comparison the contrast ratio of this page is about 7.

A higher contrast ratio is necessary for back illuminated displays; especially for negative image displays, as the human eye can easily detect light leaking through the dark background of a display. The leakage can be reduced by matching the spectral transmission of the background and spectral emission of the backlighting system correctly (especially if a colour filter is used). Both brightness and contrast depend on the type of polarizers used. For reflective displays with a positive image, low efficiency polarizers produce brighter displays with a low contrast. High efficiency polarizers produce a high contrast but will reduce brightness considerably.

#### Viewing angle

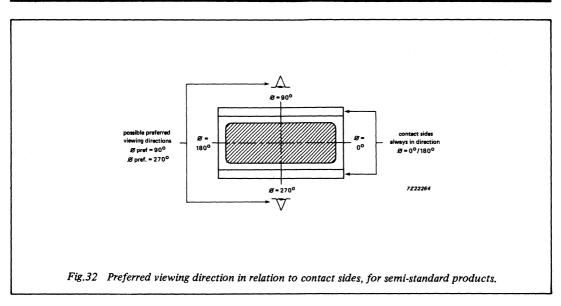

A twisted nematic LCD has a preferred viewing direction ( $\varphi_{\text{pref}}$  measured in the plane of the LCD), which is built-in during the manufacturing process by treatment of the orientation layers. For most standard applications this preferred direction is from below (6 o'clock direction) although other directions can also be manufactured.

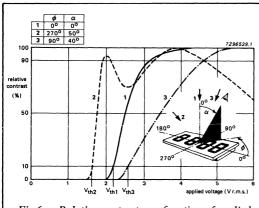

Fig.6 shows a contrast versus voltage curve from three different viewing angles  $\alpha$  which are referenced perpendicularly to the LCD. At a very low voltage the display is not visible; as the voltage is increased the pattern first appears at low elevation angles (high values of  $\alpha$ ) in the preferred viewing direction (curve 2). By further increasing the voltage the pattern becomes more visible at higher elevation angles. If the contrast is observed at a fixed drive voltage within the plane  $\varphi_{\rm pref}$  and perpendicularly to the LCD the viewing angle is  $\alpha_{\rm opt}$  and maximum contrast occurs. At higher voltages the value of  $\alpha_{\rm opt}$  becomes rather small. However,  $\alpha_{\rm opt} = 0$  can never be reached and a basic asymmetry will always remain.

The voltage at which a display becomes visible (10% of maximum contrast) at a specific viewing direction and viewing angle, is known as the threshold voltage ( $V_{th}$ ). The voltage at which contrast reaches 90% of its maximum value is known as the saturation voltage ( $V_{sat}$ ).

Voltage and contrast characteristics will vary for different liquid crystal mixtures. Most mixtures will also have a negative temperature coefficient i.e. V<sub>th</sub> decreases as the temperature increases.

Fig.6 Relative contrast as a function of applied voltage.

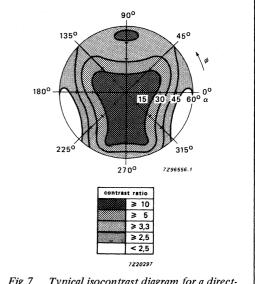

When in a plane perpendicular to  $\varphi_{\text{pref}}$ , TN LCDs have an almost symmetrical contrast. This is shown by an isocontrast diagram which is a method of illustrating the viewing cone of a display. An isocontrast diagram

is the contrast in relation to the azimuth  $(\varphi)$  and elevation  $(\alpha)$  viewing angles. Figure 7 is a typical isocontrast diagram for a TN display which has a preferred viewing direction from below (6 o'clock).

Fig. 7 Typical isocontrast diagram for a directdriven, reflective TN display, showing the variation of contrast as a function of the two components α and φ of the viewing angle.

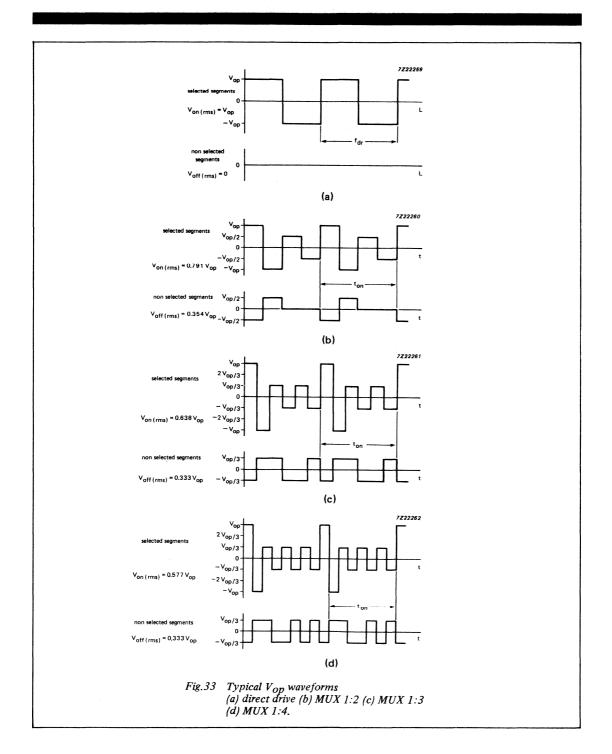

#### Response times

Typical turn-on and turn-off times for LCDs range between 50 and 100 ms at room temperature. One of the main influences upon response times is the liquid crystal viscosity. As the viscosity of the material increases with decreasing temperature the molecules become less free to move resulting in longer response times

Response times are also affected by applied voltage, drive method and liquid crystal layer thickness.

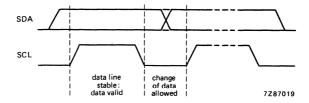

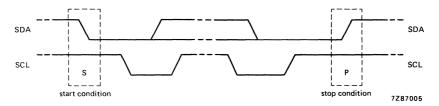

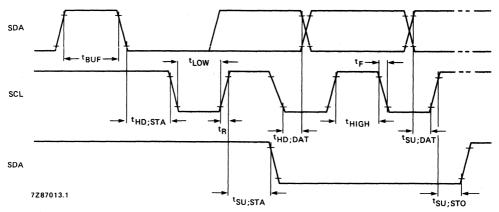

#### **DRIVING LCDs**

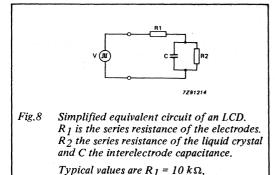

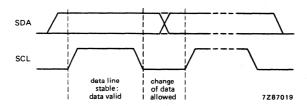

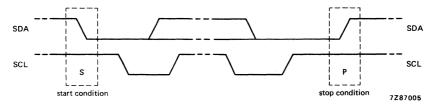

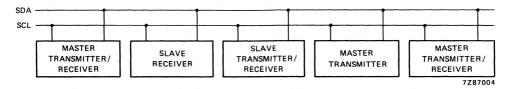

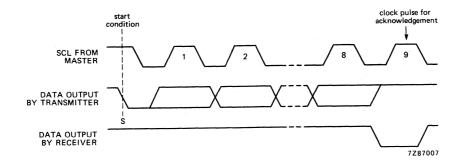

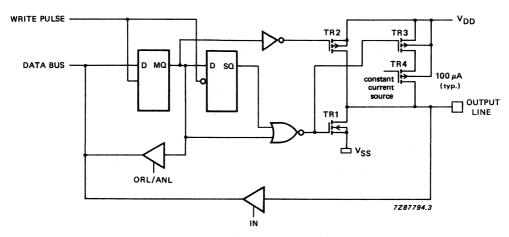

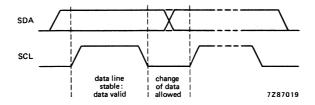

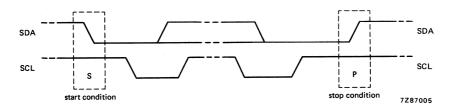

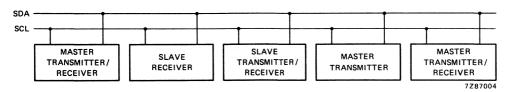

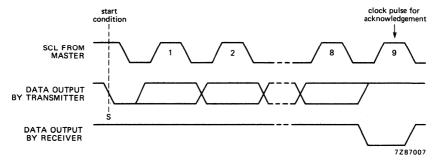

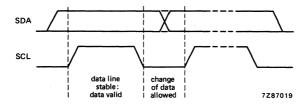

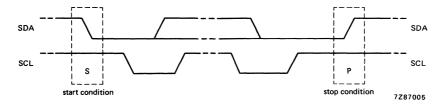

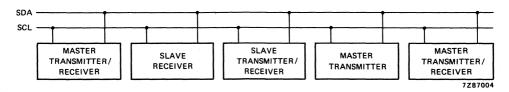

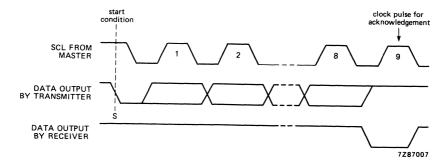

Each segment of an LCD can be considered the equivalent of an electrical capacitance with a very high parallel and low series resistance (Fig.8). The capacitance is voltage dependent as the liquid crystal molecules have anisotropic dielectric properties. Applying a DC voltage will cause electro-chemical reactions which shorten the life of the LCD. For this reason, the drive voltage must be alternating with a maximum permissable DC component of 100 mW. The optical effect then produced in a display depends approximately on the rms value of the drive voltage.

The frequency of the drive voltage must be at least 30 Hz to prevent display flicker. At this frequency and a drive voltage just above the saturation voltage, typical current consumption is approximately 1.5  $\mu$ A per square centimetre of the activated display area.

$R_2 = 1 M\Omega/cm^2$ ,  $C = 1.5 nF/cm^2$ .

The current consumption increases in direct proportion to the drive frequency. An upper frequency limit is set by coupling and relaxation effects which cause ghosting and irregular contrast in the display. These effects must be considered, especially in the layout of large and complex displays. The upper frequency limit is approximately 200 Hz.

Possible interference effects with lighting systems should also be considered when deciding on the drive frequency to be used.

#### **Direct Drive**

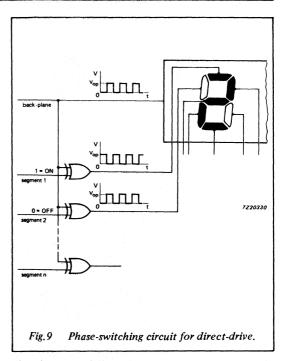

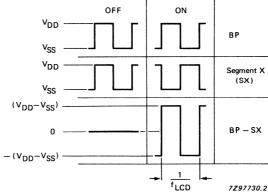

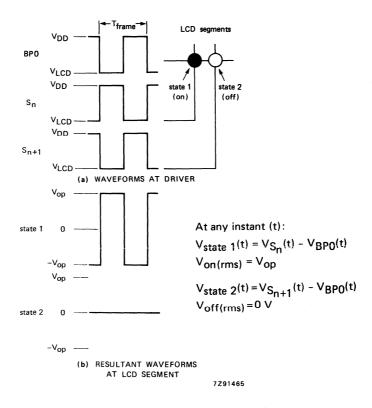

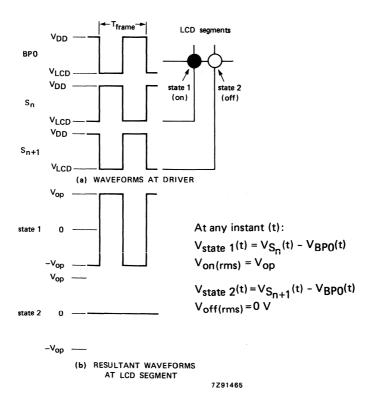

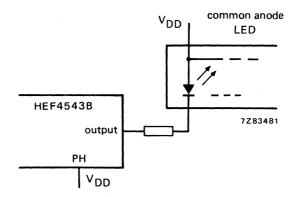

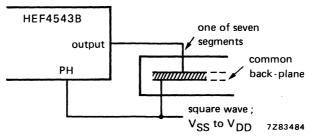

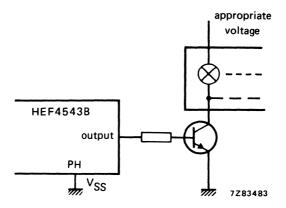

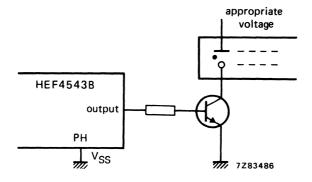

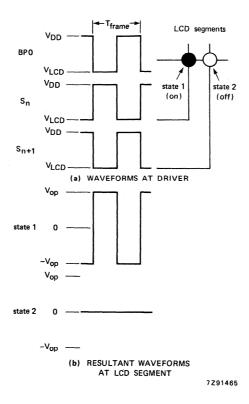

A direct (or static) drive LCD has a separate connection and driver for each segment and one for the common back-plane.

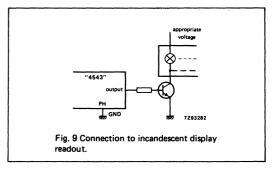

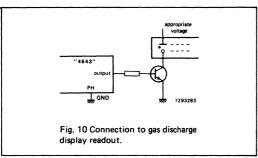

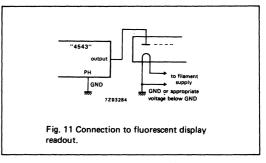

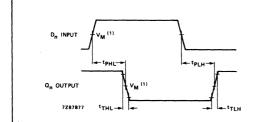

The back-plane of a direct drive display is usually driven by a square wave having a peak-to-peak value (V<sub>op</sub>) that is above the saturation voltage (V<sub>sat</sub>). To select a segment, the inverse of the back-plane waveform is applied to the appropriate electrode. This produces an rms voltage between the back-plane and segment electrodes which is equal to Vop. The backplane voltage waveform is also applied to all nonselected segments which results in a net zero voltage across them. It should be noted that a symmetrical square wave must be used, otherwise undesirable DC components will be applied to the liquid crystal. Fig. 9 illustrates a typical direct drive circuit with exclusive-OR gates controlling the voltage to the different segments. Individual segments are selected by switching the appropriate segment control line HIGH. This will have the effect of inverting the backplane voltage applied to the segment. The control lines of non-selected segments are LOW so that no inversion takes place.

The advantage of direct drive are broad temperature ranges, wide viewing angles, fast response times and insensitivity to driving voltage tolerance. However, the number of connections and driving circuits needed can become very large for complex displays.

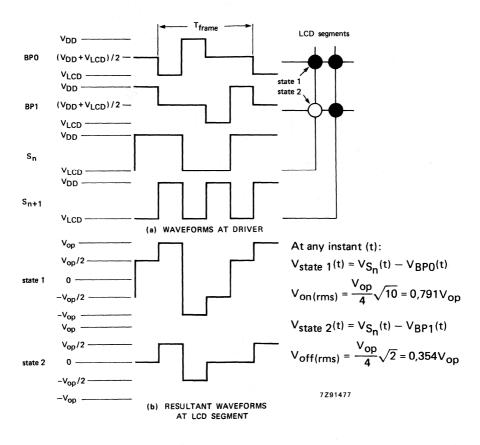

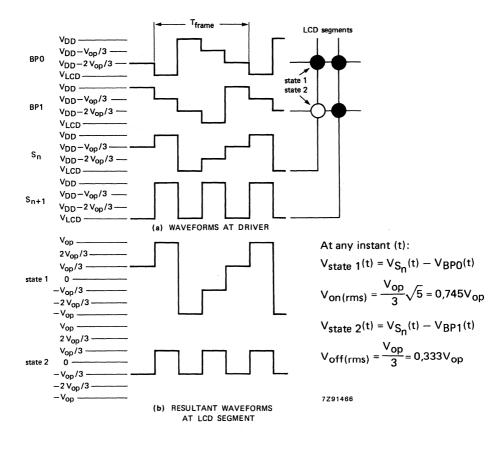

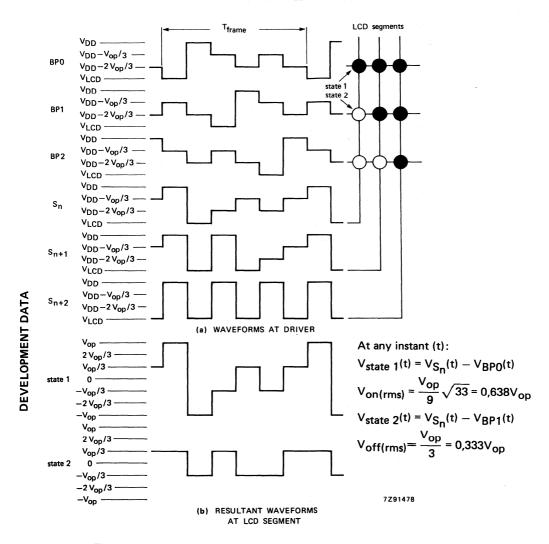

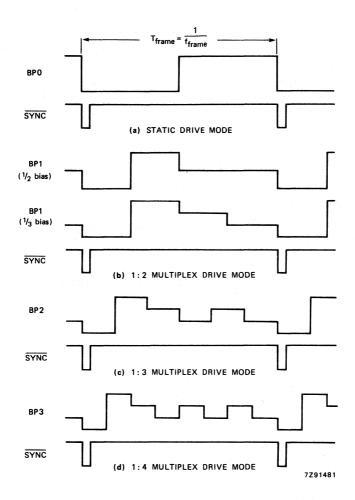

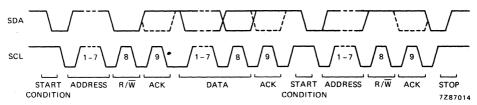

#### **Multiplex Drive**

In high information density displays, such as a dot matrix, it is difficult or impossible to connect each dot or segment individually to an edge contact. The large number of contacts and drivers required could lead to low reliability and high cost. Therefore, it is necessary to use multiplex drive.

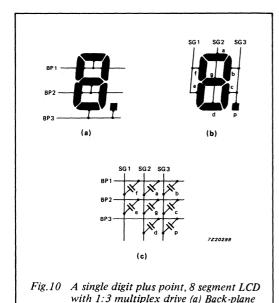

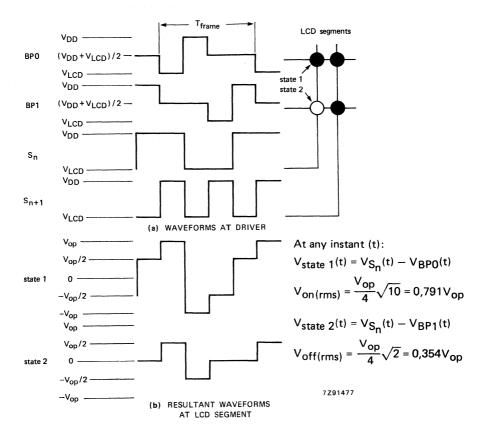

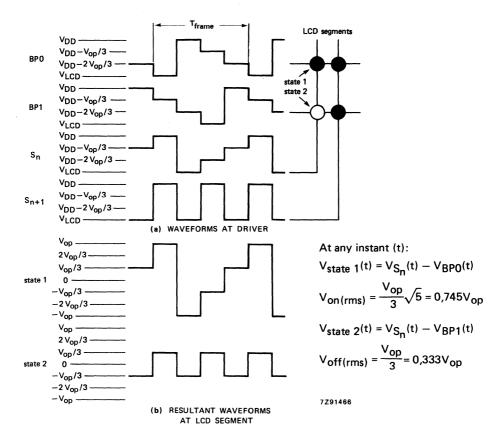

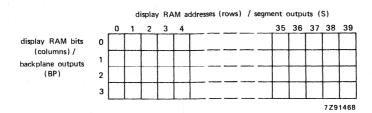

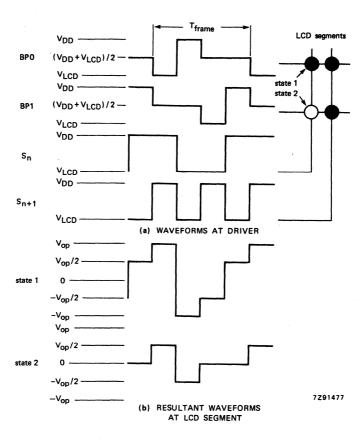

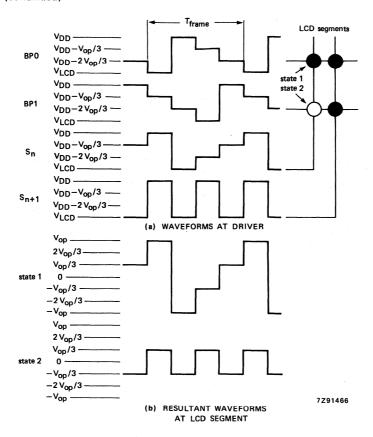

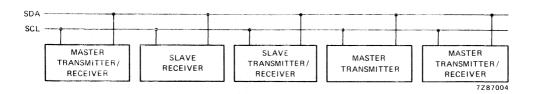

Multiplex drive electrodes are arranged in the form of a matrix. Segments are connected in groups and the back-plane is split into several commons so that every segment in a group has a different back-plane. A segment is then no longer identified by an individual external contact but by a group contact and a specific back-plane. The multiplex ratio is defined as 1:N, where N is the number of back-planes, or segments, per group.

Fig. 10 illustrates the segment to back-plane assignment for a seven segment digit using 1:3 multiplex drive. The number of contacts needed has been reduced from the nine used in direct-drive, to six. Fig. 10(c) shows the equivalent circuit with each segment being represented by a capacitor.

The reduction in the number of contacts required by using multiplexing can be dramatic. A segment display having a multiplex ratio of 1:N and a total of M seg-

(c) Equivalent circuit.

electrodes (b) Segment grouping

# connections. For example:

a 40 segment display requires 41 connections in direct drive but, by using a 1:4 multiplex drive, the number of connections is reduced to:

ments can be addressed using as few as M/N + N

$$40/4 + 4 = 14$$

a dot matrix display with 20 000 elements (pixels)

i.e. 100 rows and 200 columns can be controlled with only 300 connections (number of rows + number of columns) rather than the 20 001 connections that would be needed for direct drive.

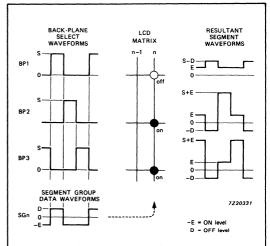

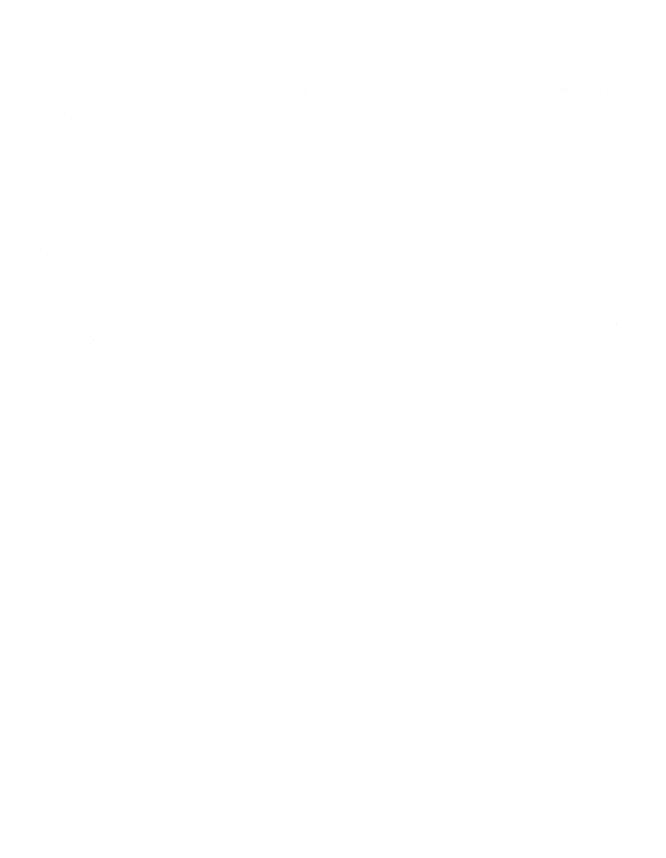

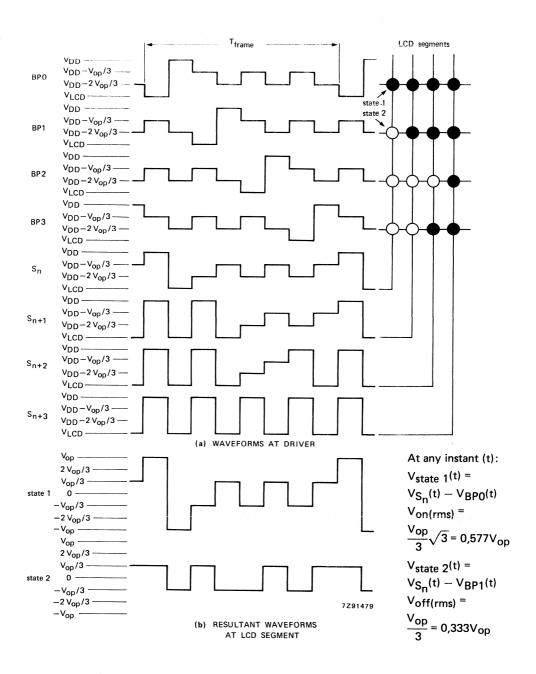

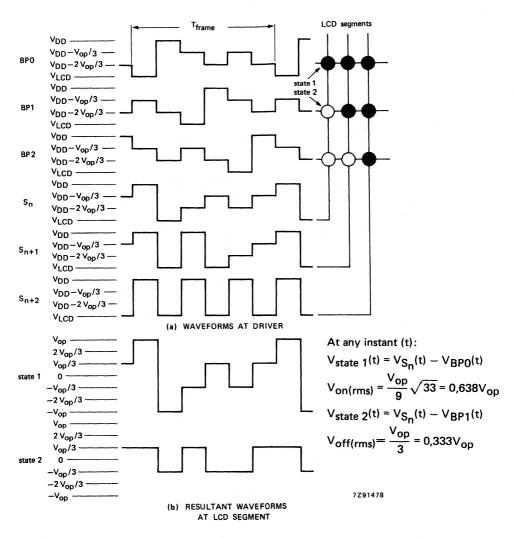

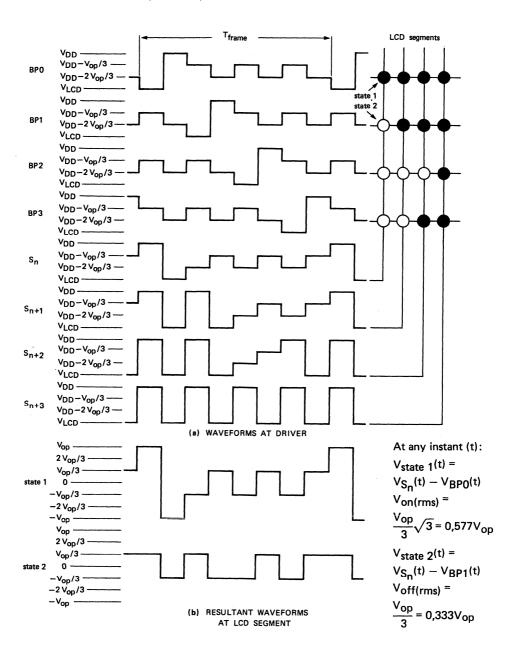

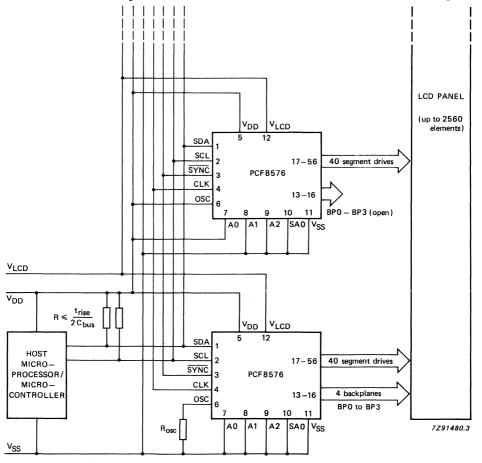

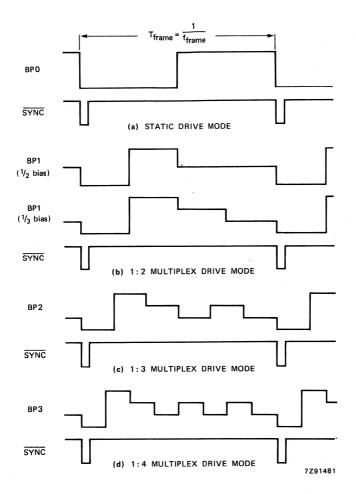

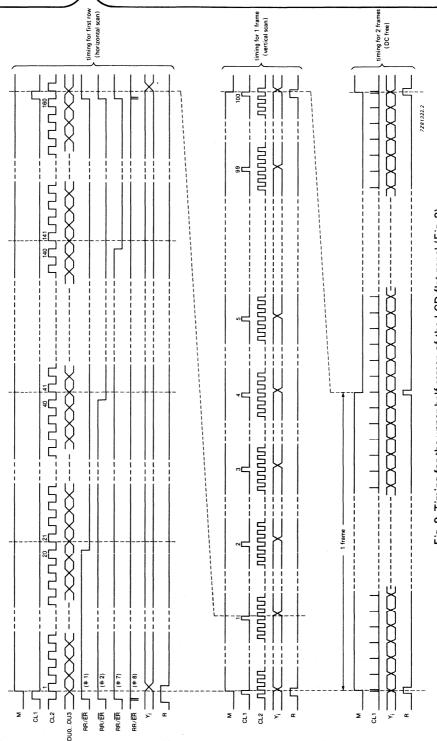

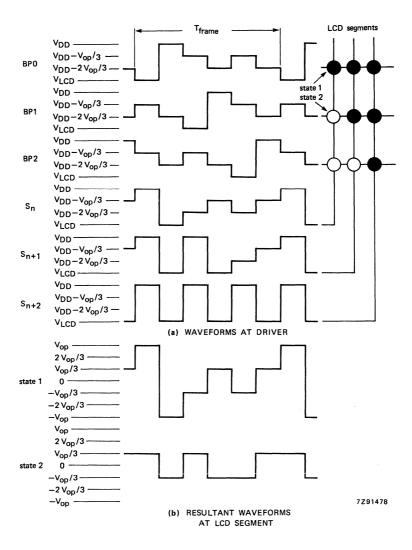

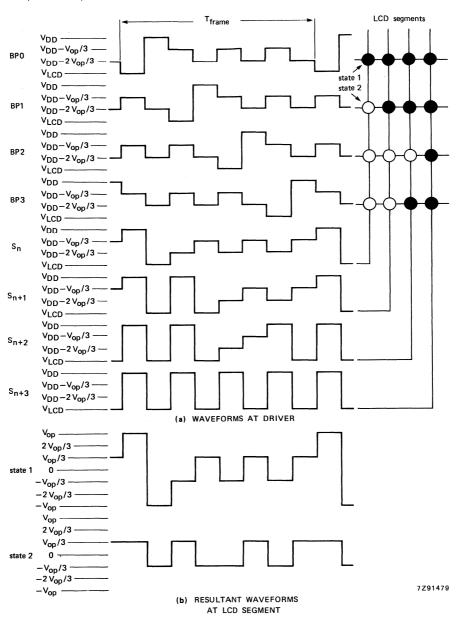

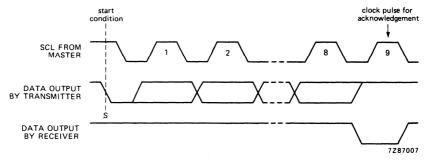

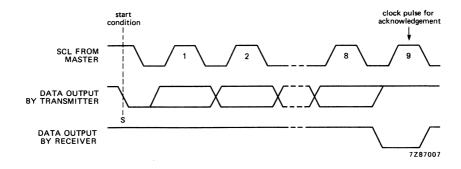

An individual segment is selected by a combination of the back-plane and segment group signals. Fig.11 shows a simple example of matrix waveforms. Each back-plane is selected in sequence and whether or not a segment is selected is determined by the level of the segment group voltage when the corresponding back-plane is addressed. The waveforms illustrated have net DC components which could cause electromechanical degradation of the liquid crystal. In practical addressing schemes, the net DC component is eliminated by inverting both the back-plane and segment group waveforms alternately.

Fig.11 Row and column multiplexing waveforms for a display showing the voltage waveforms across individual elements.

Fig.11 shows that all of the elements receive a voltage. This means that the voltage at which non-selected elements should remain OFF has been raised above zero. The ratio of the ON to the OFF voltage (discrimination) decreases as the multiplex ratio increases (see Table 1) and the non-selected elements will become slightly visible. The discrimination can be optimised up to a certain limit, by increasing the number of multiplex levels.

Table 1 shows that the largest relative profit is obtained when going from direct drive to MUX 1:2 drive The number of connections is approximately halved but a reasonably good discrimination is obtained (2.24). Which is why MUX 1:2 is popular for displays up to  $100 \dots 150$  segments (higher MUX rates would give little or no advantage, while reducing the contrast relatively fast).

Table 1 Discrimination and number of connections compared to the multiplex rate

| multiplex ratio                    | 1:1      | 1:2  | 1:3 | 1:4  | 1:8  |

|------------------------------------|----------|------|-----|------|------|

| discrimination,                    |          |      |     |      |      |

| $\frac{V_{on(rms)}}{V_{off(rms)}}$ | <b>∞</b> | 2.24 |     | 1.73 | 1.45 |

| number of                          | 121      | 62   | 43  | 34   | 23   |

| connections                        |          |      |     |      |      |

| required for a                     |          |      |     |      |      |

| display having                     |          |      |     |      |      |

| 120 segments                       |          |      |     |      |      |

# ELECTRO-OPTICAL CHARACTERISTICS OF MULTIPLEXED LCDs

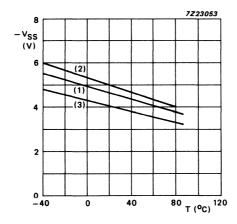

Most applications require the OFF elements to remain invisible up to a certain viewing angle  $(\alpha)$ . Which means, in order to keep the OFF voltage below the threshold  $(V_{th})$  the value of the operating voltage  $(V_{op})$  must not exceed a maximum criteria (Fig.6). However, for ON elements a minimum contrast at a different viewing angle is required, which calls for a value of  $V_{op}$  that exceeds a minimum criteria. Since  $V_{th}$  is temperature dependent, both ON and OFF criteria of  $V_{op}$  vary with temperature (see Fig.12 for MUX rates 1:2 and 1:8). The area between the ON and OFF criteria is the recommended operating area because it represents invisible OFF segments and ON segments with sufficient contrast.

Fig.12 Typical recommended voltage areas for (a) 1:2 (b) 1:8 multiplex drive. At the lower boundary of each area the off segments become faintly visible at a viewing angle  $\alpha = 40^{\circ}$ ,  $\phi = 270^{\circ}$  while the ON elements are visible with a contrast better than 2 at  $\alpha = 0^{\circ}$ .

At low multiplex ratios satisfactory operation over a wide temperature range can be obtained with a fixed value of  $V_{op}$ . However, in order to obtain a constant viewing cone throughout the same temperature range at higher multiplex ratios,  $V_{op}$  has to be temperature compensated to allow for the negative temperature coefficient of  $V_{th}$ .

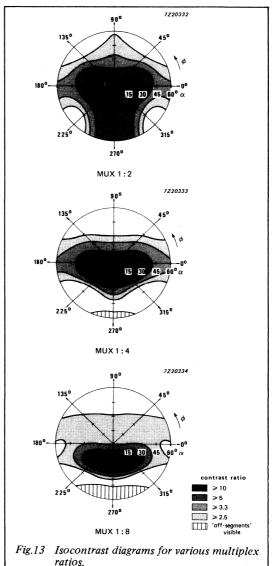

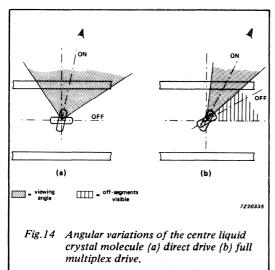

Besides its effect on the operating voltage and temperature range, increased multiplexing also narrows the viewing cone (Fig.13).

The effect of OFF segments being visible depends upon the type of display pattern. In a segment display incorrect information may be displayed and the multiplex ratios are therefore, normally limited to 1:8. In character or full dot matrix displays visible OFF segments can result in somewhat darker background which is disturbing but the information is still correct and readable up to a multiplex ratio of about 1:100. Satisfactory operation at higher multiplex ratios is obtained using advanced technologies like STN displays.

#### **DERIVED TECHNOLOGIES**

Super Twisted Nematic (STN) displays

The main limiting factor in the use of a multiplexed TN display is the gradual slope of the contrast as a function of the voltage curve. It has been discovered that this curve can be made much steeper by increasing the twist angle of the crystal beyond 90° to a value that ranges from 180° to 270°.

The larger twist angle is achieved by using a special cholesteric doped nematic liquid crystal. The cholesteric molecules have a helical screw structure (Fig. 2) which helps to ensure that all liquid crystal molecules twist in the same direction and have the same stable state.

STN displays use birefringence effect which introduces wavelength dependence and a characteristic colour into the display. With optimized polarizer angles the display will e.g. appear blue on a bright background (blue mode) or bright on a yellow background (yellow mode). STN displays can produce images with a good contrast over wide viewing angles at multiplex rates of 1:100 or higher.

#### Guest-Host Display (GHD)

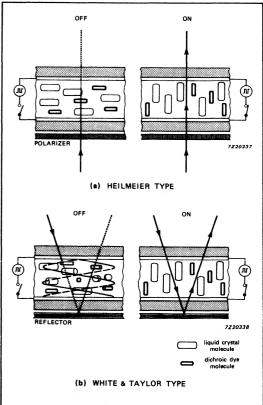

Two problems associated with TN displays are the angular dependence of the contrast and the relatively low brightness. These are both caused by the use of two polarizers. An alternative type of display is the Guest-Host Display (GHD) which works with one or no polarizers. In GHDs the molecules of a dichroic dye (guest) are dissolved into the nematic liquid crystal (host). The guest molecules always align themselves parallel to the molecules of the liquid crystal.

When there is no voltage applied the molecules are aligned parallel to the display surface (OFF state) certain wavelengths of the incident light are absorbed by the dye and the display appears coloured. When sufficient voltage is applied the molecules will align perpendicular to the display (ON state), the dye no longer absorbs the light and the display appears bright (Fig.15). GHDs typically have bright segments on a coloured background, the colour of which depends on the dye and can include black.

Fig. 15 Operation of a GHD (a) Heilmeier (b) White and Taylor.

There are two main types of GHD:

- Heilmeier (Fig.15a). This display requires a front polarizer for good legibility and must have good backlighting or be viewed in good ambient light conditions.

- White and Taylor (Fig.15b). This display is optimized for reflective operation because it does not require polarizers and produces very bright segments against a coloured or grey background.

The advantage of guest-host displays over twisted nematic displays is the very wide and regular viewing cone. Disadvantages are the higher operating voltage and poor multiplexibility.

#### **CONNECTING TECHNIQUES**

The terminals of an LCD are Indium/Tin Oxide and are situated on at least one side of the cell.

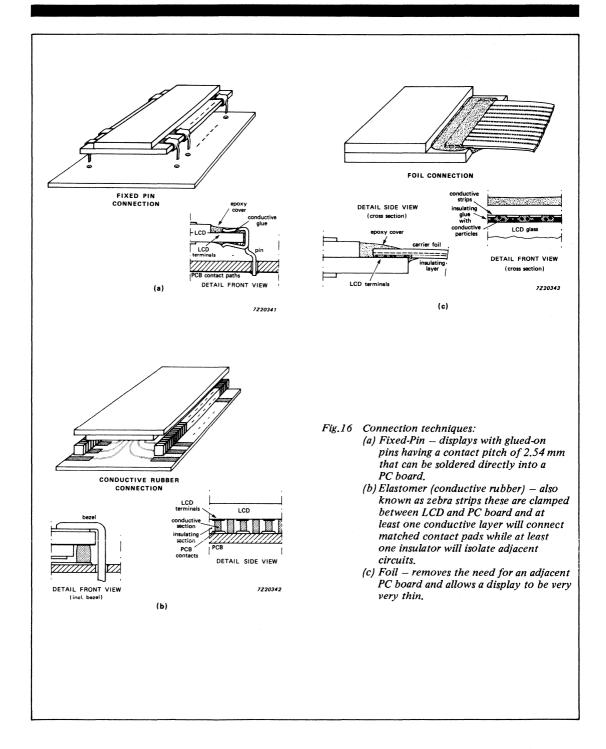

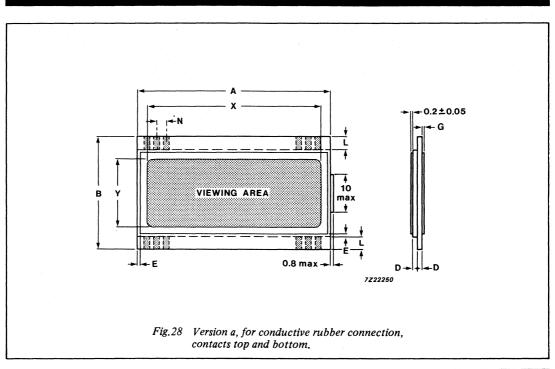

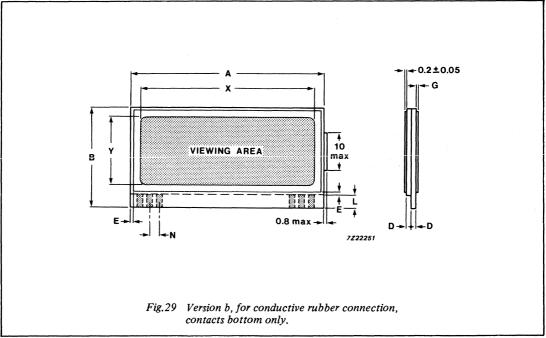

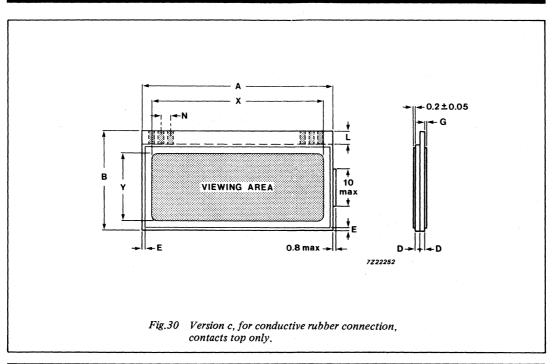

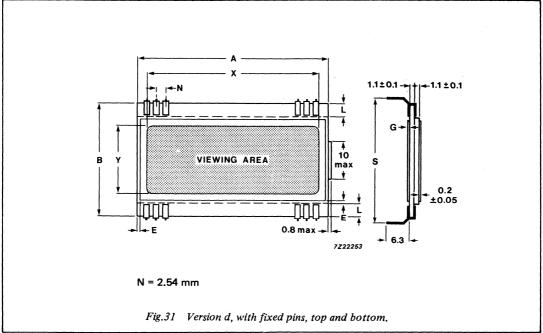

The three main methods used to electrically connect LCDs are: fixed pins, conductive rubber (elastomer) strips and foil.

Fixed pins are glued directly onto the LCD which can then be soldered directly on to a PC-board or connected via snap-on sockets (Fig.16(a)). Fixed pins are suitable for LCDs with a relatively low number of connections and the glass length is sufficient to accommodate the required pins. However, they provide a reliable method of contact.

Elastomer connectors consist of alternate conductive and insulating sections that support the LCD and connect it to the PC-board (Fig.16(b)). The contacts of the LCD are on the underside of the top glass and these connect to the PC-board via the conducting sections of the elastomer strip. Contact is maintained by a mounting bezel or clamp which squeezes the LCD, elastomer strip and the PC-board together. Care must be taken to ensure that a constant pressure is maintained over all the connections which requires special attention in long displays. Without optical alignment a contact pitch down to about 1 mm can be used and down to about 0.5 mm with optical alignment.

Foil connectors (Fig.16(c)) provide a flexible method of connection for LCDs. They consist of parallel conductors mounted on a foil which is glued directly on to the LCD; the contact area is thus sealed from the atmosphere. Connection pitches at each end of the foil can vary and the drivers can be mounted on a remote printed circuit-board which is an advantage where a very thin display or back-lighting is required.

#### **MOUNTING & ILLUMINATION TECHNIQUES**

Reflective and transflective displays should be mounted as close as possible to the front surface of the equipment to gain maximum illumination from the ambient light. When choosing a mounting position the viewing angle and isocontrast diagram published in the LCD data sheet must be considered. Auxiliary front lighting for a reflective display should be at an angle close to the normal viewing direction to minimise reflection and shadow effects.

Mounting pressure applied to LCDs using elastomer connectors should be as even as possible and pressure on the seal or viewing areas must be avoided. Glass or non-birefringent plastic should be used to protect the frontpolarizers from scratches and humidity.

#### **Back-lighting**

Back-lighting of a transflective display is necessary to maintain legibility under poor environmental light conditions.

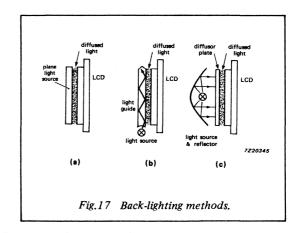

The main methods used for LCD back-lighting are listed below:

- Electro-luminent light-source; has the advantage that it is very thin and emits a diffuse and evenly distributed light. However, its luminance is low, it requires a supply of 100 to 200 V at a few hundred Hz and it has a limited life (Fig.17(a)).

- Light guide; a point source such as an LED or a linear source such as a fluorescent tube is distributed by a light guide using total reflection.

Its construction can be flat so little space is required behind the LCD. However, uniform light distribution can be difficult to obtain and light loss can be considerable (Fig.17(b)).

- Light box; an LED, halogen or fluorescent light is distributed by a light box; this light source is very effective but needs considerable space immediately behind the display (Fig.17(c)).

Any form of back-lighting for LCDs requires considerably more power than is used by an unlit display. This is a limiting factor when using a battery power supply.

# Liquid crystal display

# LCD modules

|                                                      | <br>  |             |                 |   | · |     |          |

|------------------------------------------------------|-------|-------------|-----------------|---|---|-----|----------|

|                                                      |       |             |                 |   |   | pag | зe       |

| Introduction to LCD modules                          | <br>  |             | · · · · · · · · |   |   | 3   | 33       |

| Segment display modules                              |       |             |                 |   |   |     |          |

| Character display modules Dot matrix display modules | <br>· | • • • • • • |                 | / |   | 3   | 14<br>14 |

## LCD modules

#### INTRODUCTION TO LCD MODULES

An LCD module is a liquid crystal display complete with driving circuitry, and in many applications also decoding and control circuitry which assists interfacing.

Typical applications for LCD modules include industrial display equipment, pocket VDUs, portable computers, telephony equipment, typewriters and point of sales equipment.

The internal inter-connection between driving circuitry and display can be elastomer (zebra-stripes) or flex-foil. One of the advantages of an LCD module over a loose display is that less external connections are required, allowing a mounting location which is remote from the control circuit.

The use of a complete LCD module in display equipment means a great deal less time in designing the display into the equipment, as all the driving circuitry is internal and interface to a microprocessor is the design engineers only concern.

All of our modules are light and compact and can be easily mounted into display equipment. They have a good contrast over wide viewing angles.

We offer our modules in three display modes which are:

- (i) segment display modules

- (ii) character display modules

- (iii) dot matrix display modules

For each mode we have standard types available which are listed in Table 2.

#### SEGMENT DISPLAY MODULES

#### Features

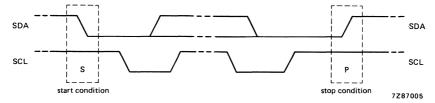

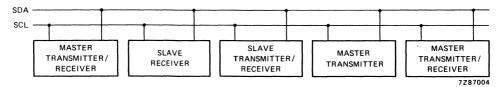

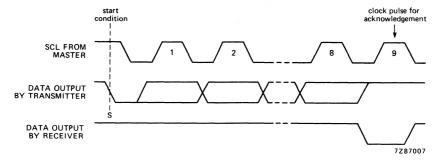

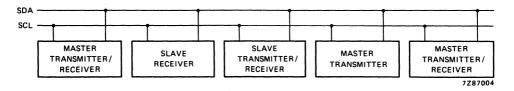

- Serial interface e.g. C-bus and I<sup>2</sup>C-bus

- Low MUX rate hence good contrast and viewing angle, especially in high ambient light conditions

- Low drive voltage

- Light, compact and easy to mount

#### Description

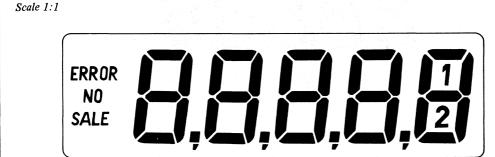

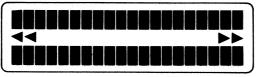

Segment display modules are intended for numeric applications (though the design can include some fixed symbols). In comparison to character types the restriction in data representation allows low multiplex rates (up to MUX 1:4), good contrast over wide viewing angles and low driving voltage. A typical application for segment display modules is in telephone sets for displaying the dialled number.

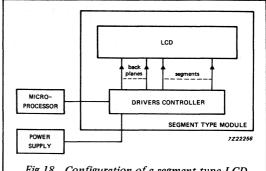

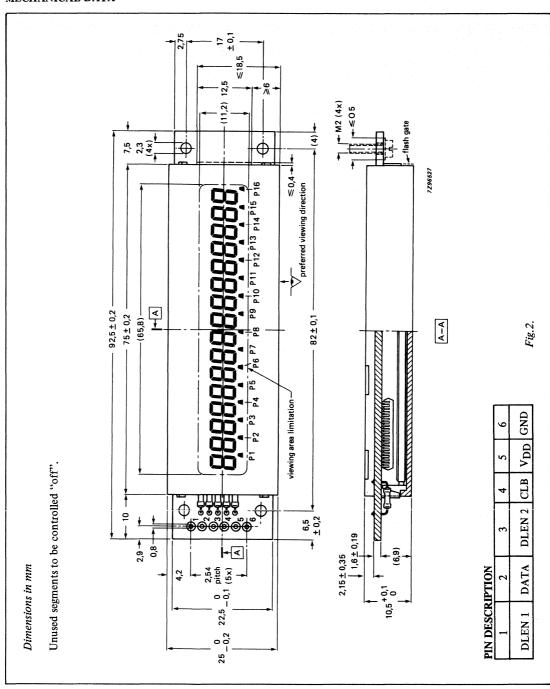

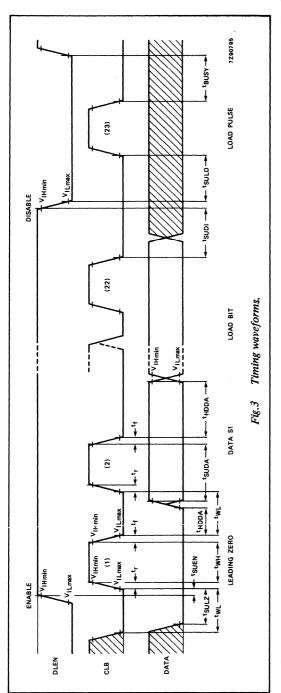

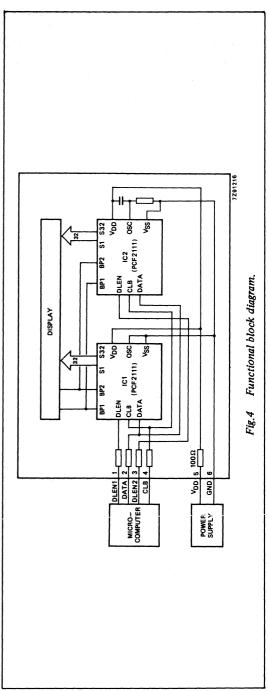

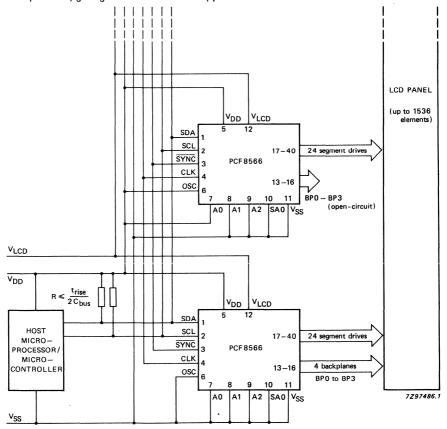

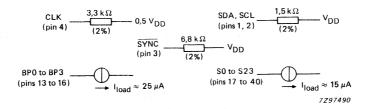

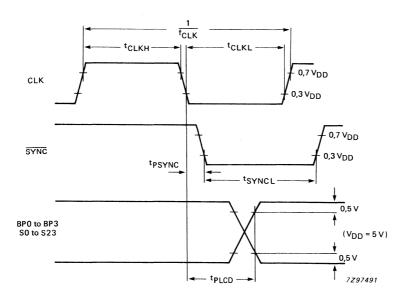

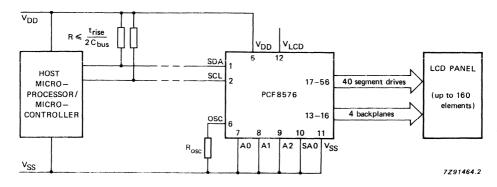

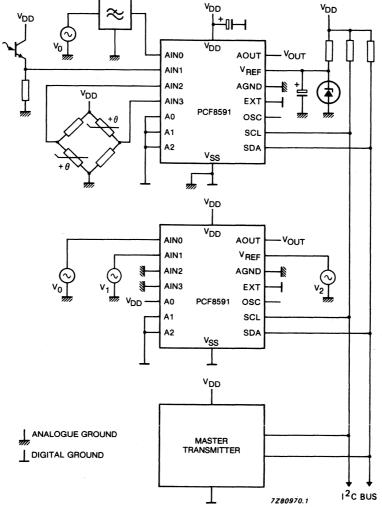

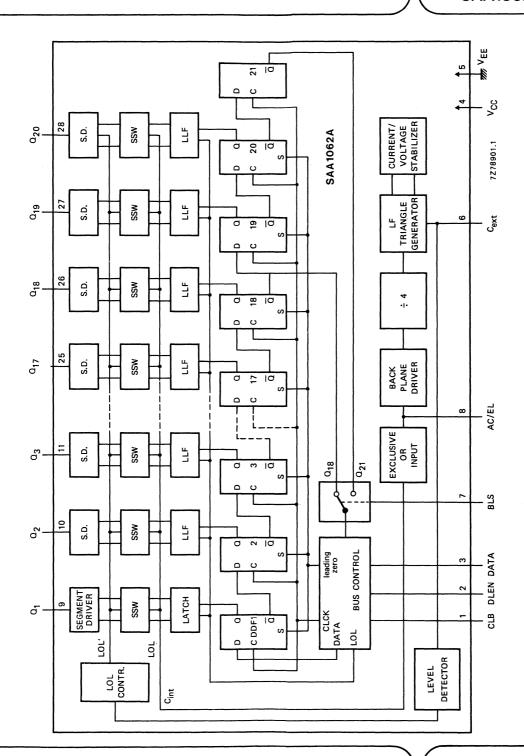

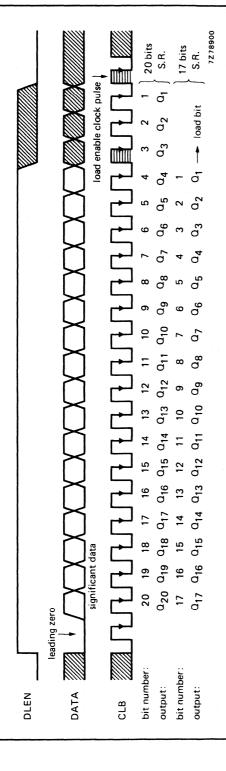

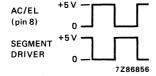

Fig.18 Configuration of a segment type LCD module.

Table 2 TN LCD module types

| DESCRIPTION                 | ILLUM, MODE   | CLASS      | TYPE NUMBER |

|-----------------------------|---------------|------------|-------------|

| 1-line, 16-digit            | reflective    | segment    | LTM233R-10  |

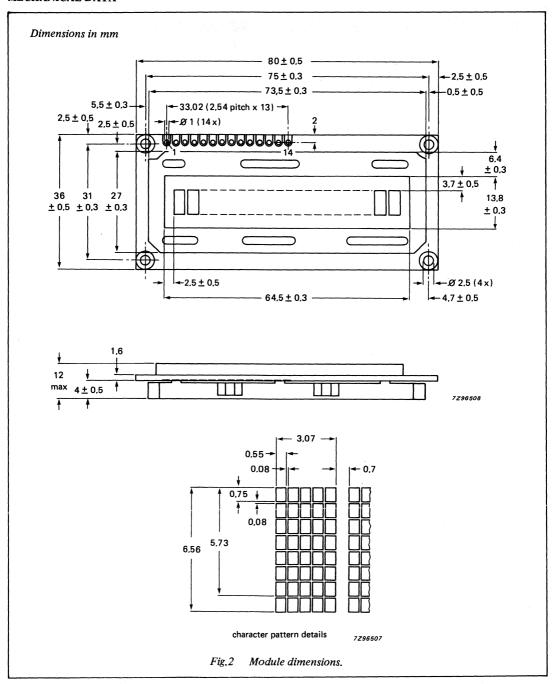

| 1-line, 16-character        | reflective    | character  | LTN111R-10  |

|                             | transflective |            | LTN111F-10  |

| 2-line, 16-character        | reflective    | character  | LTN211R-10  |

|                             | transflective |            | LTN211F     |

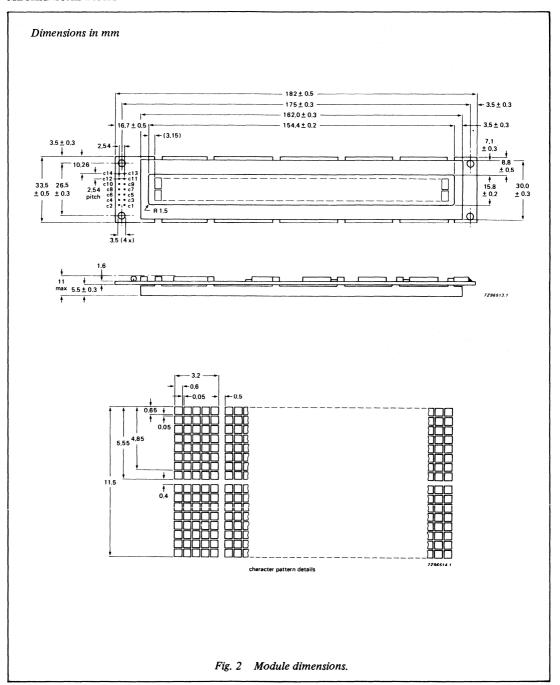

| 2-line, 40-character        | reflective    | character  | LTN241R-10  |

| 240 × 64 dot, full graphic  | reflective    | dot matrix | LTG201R-10  |

| 640 X 200 dot, full graphic | transflective | dot matrix | LTG401F-10  |

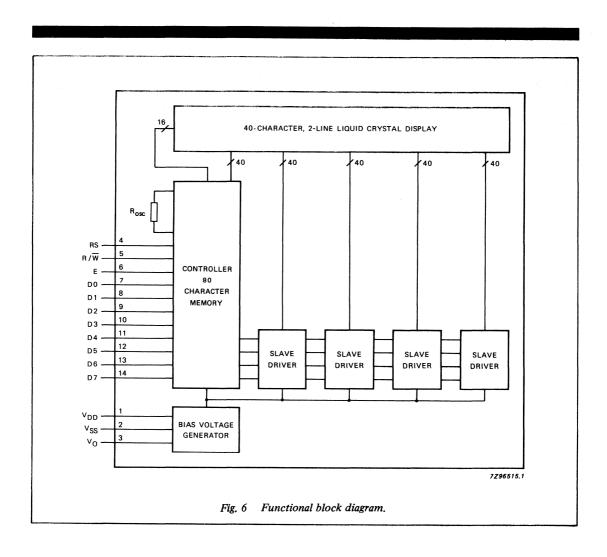

#### CHARACTER DISPLAY MODULES

#### Features

- Interface with either 4-bit or 8-bit parallel data input (ASCII)

- Built in controller that includes a character generator, and LCD driver functions

- Good legibility in bright light

- Light and compact and easy to mount

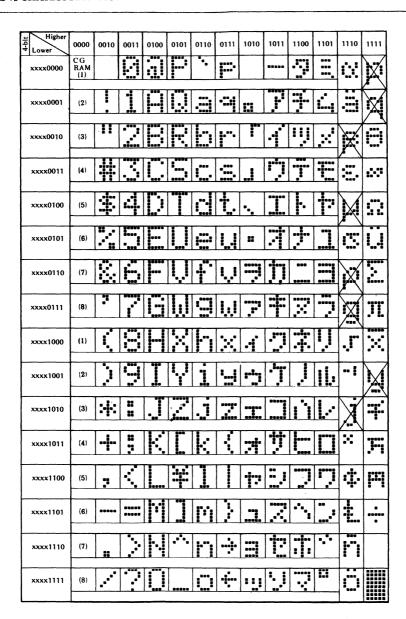

#### Description

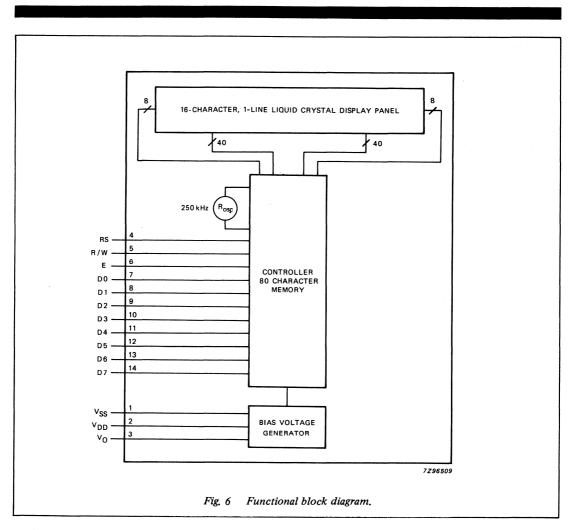

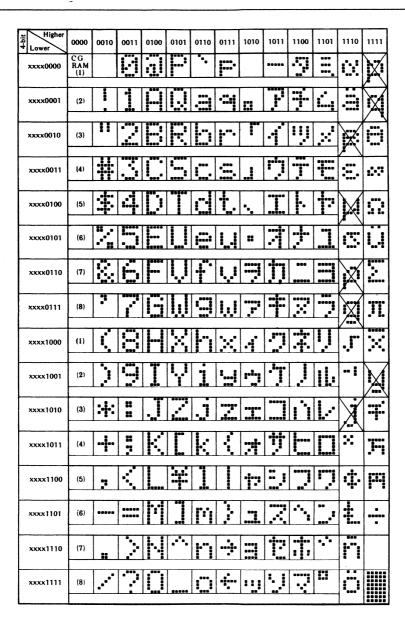

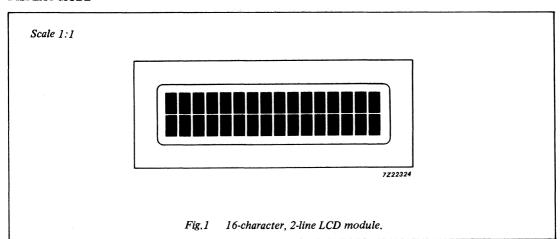

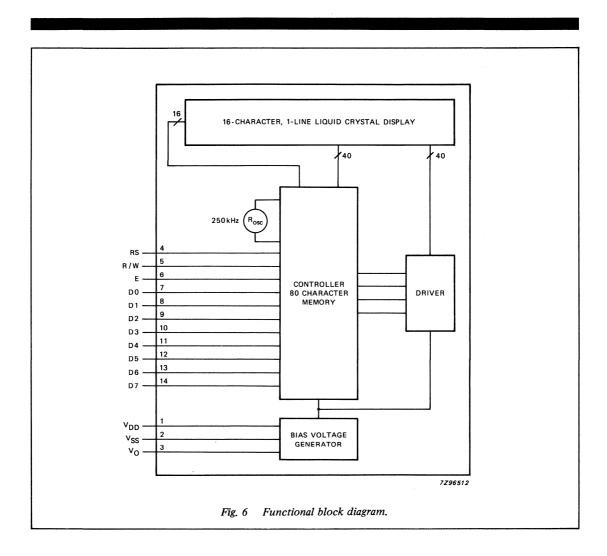

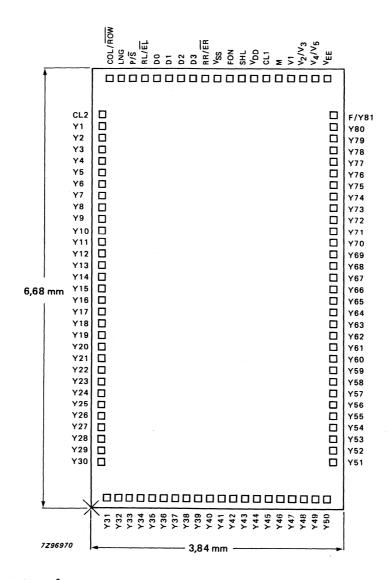

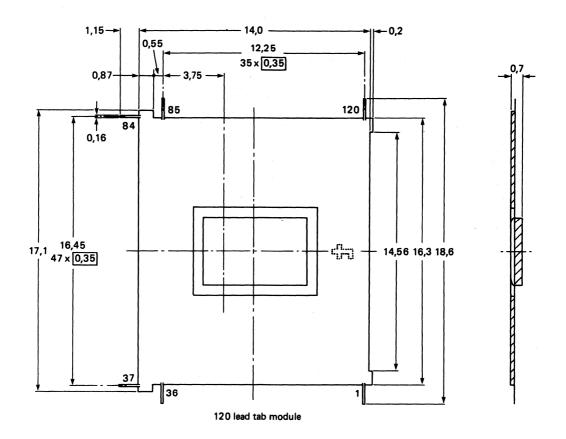

Character liquid crystal display modules (also known as alpha-numeric displays) are light and compact modules with a controller including a character generator, LCD driver LSI-ICs and a character type LCD cell mounted on a single printed circuit board. The built in character generator makes the design engineers task easier when incorporating one of our character modules within his equipment. It is capable of generating 168-alphanumeric, Japanese characters and symbols (160 fixed characters and 8 user programmable characters).

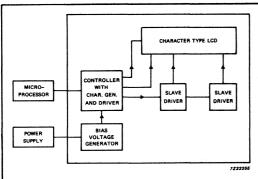

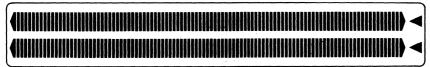

Fig. 19 Configuration of a character type LCD module,

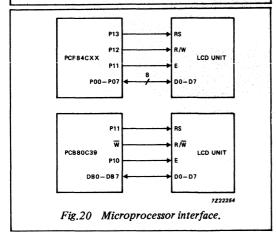

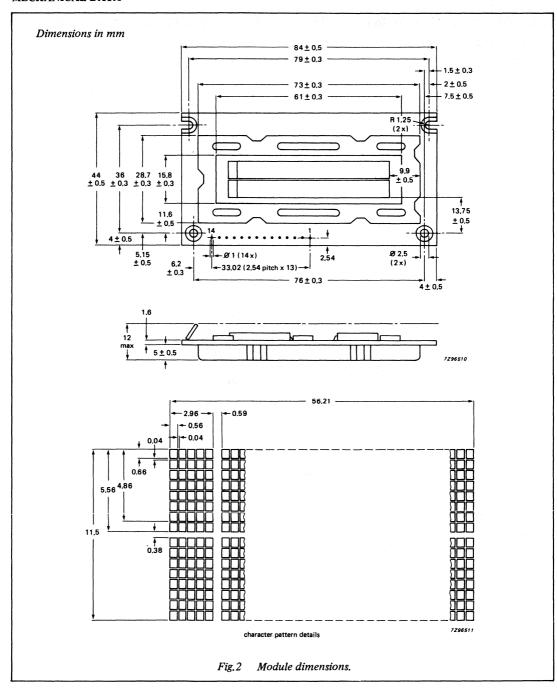

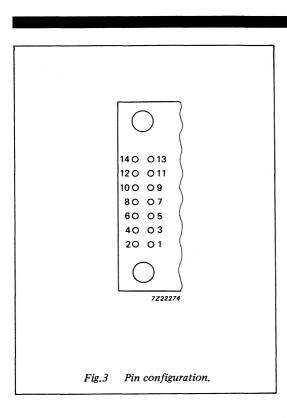

Our character display modules are offered with 1, 2 or 4-lines of characters and a character font of  $5 \times 8$  ( $5 \times 7$  dots + cursor). They can be interfaced with a 4- or 8-bit parallel microprocessor and have a 1:16 multiplex drive ratio (refer to technical publication 238 for further details on character display modules).

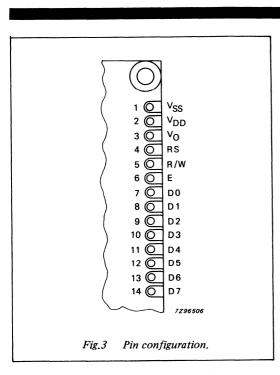

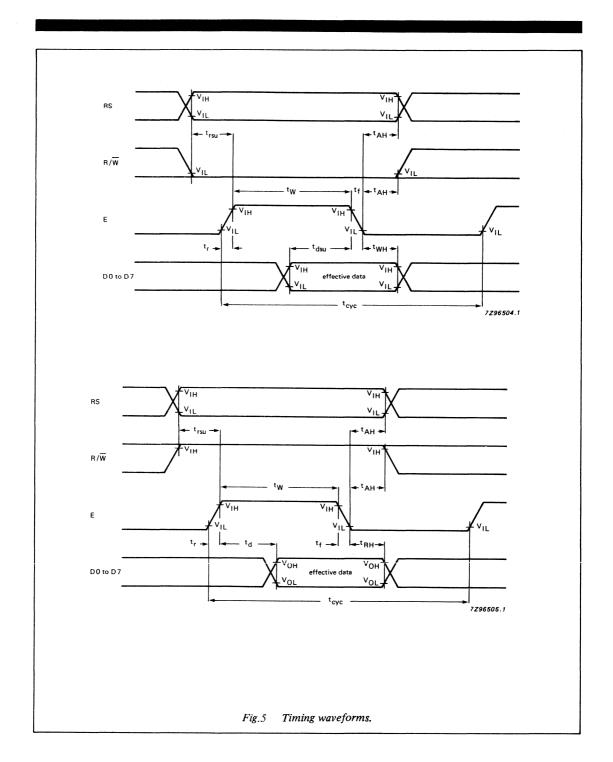

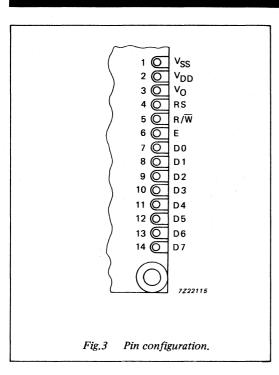

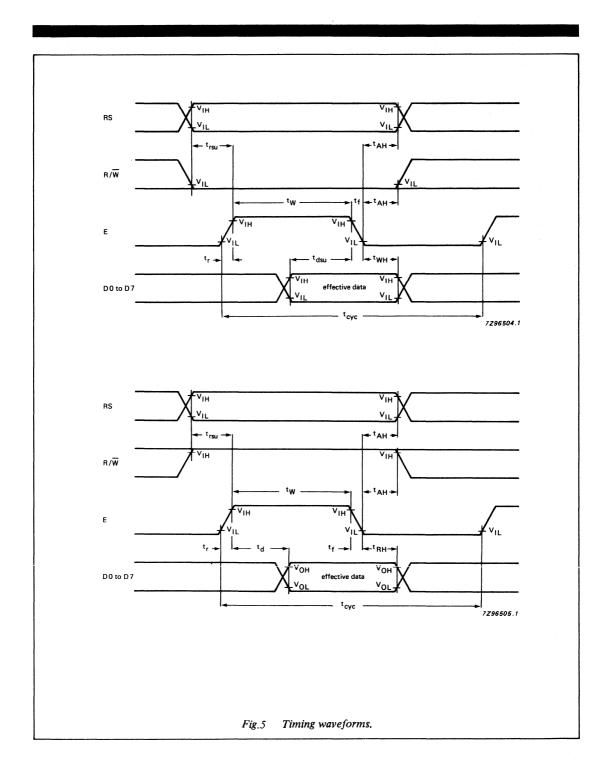

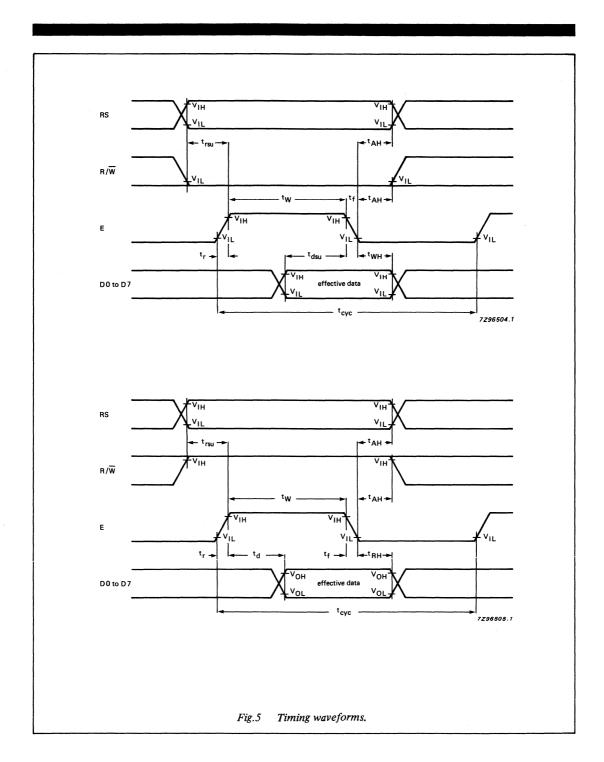

#### i) Interface signals

| RS       | register select   |

|----------|-------------------|

| R/W      | read/write select |

| E        | enable read/write |

| D0 to D7 | input output data |

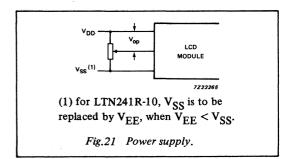

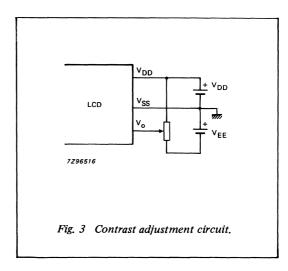

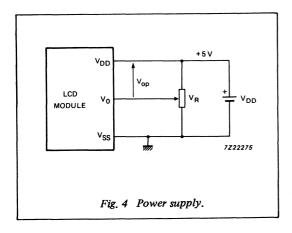

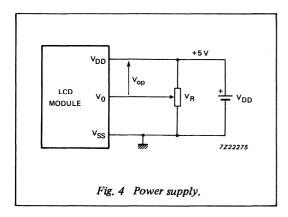

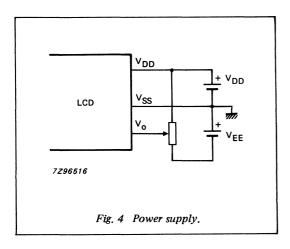

#### ii) Supply voltages

| $v_{ m DD}$ | positive supply voltage for logic         |

|-------------|-------------------------------------------|

| $v_{SS}$    | negative supply voltage for logic         |

|             | (logic ground)                            |

| $v_{O}$     | contrast adjustment voltage:              |

|             | operational LCD voltage,                  |

|             | $V_{op}$ equals $V_{op} = V_{DD} - V_{O}$ |

# DOT MATRIX DISPLAY MODULES Features

- Full dot graphic display capability

- Good legibility in bright light

- Light and compact and easy to mount

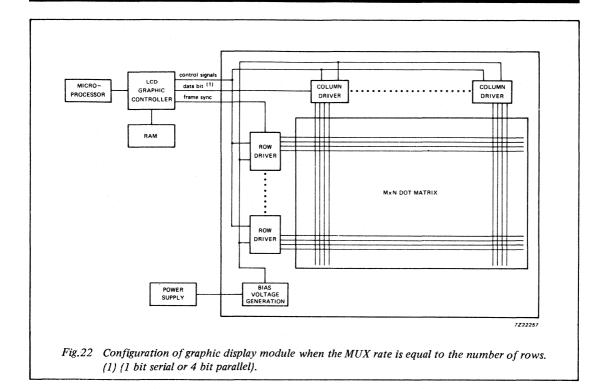

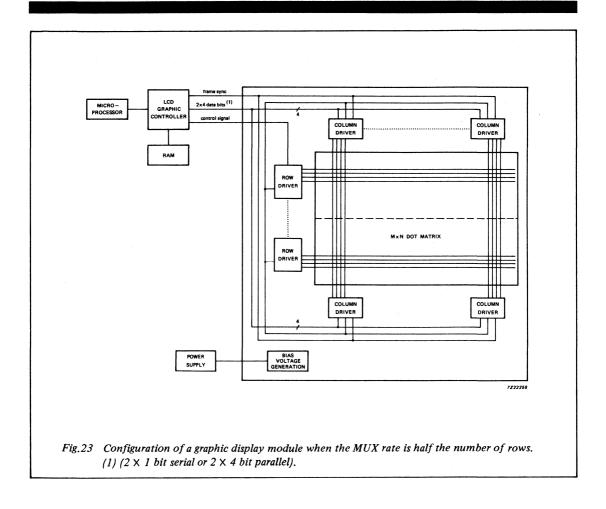

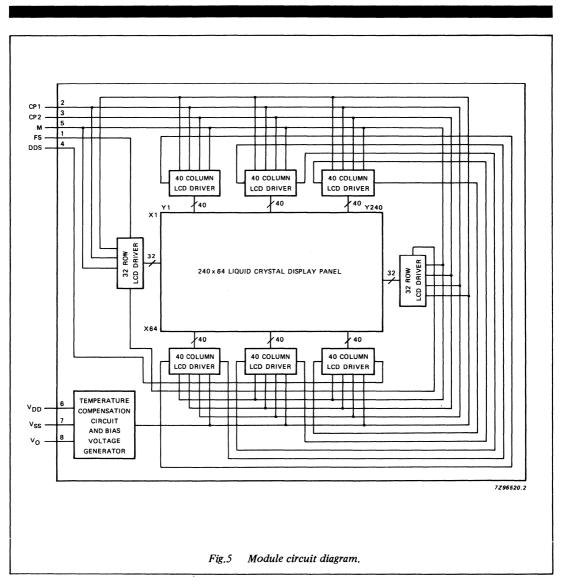

#### Description

Dot matrix LCD modules (also known as flat panels) are capable of displaying a wide variety of data as each individual dot can be controlled ON or OFF. The dot matrix LCD module is ideal for displaying diagrams, graphs, and text.

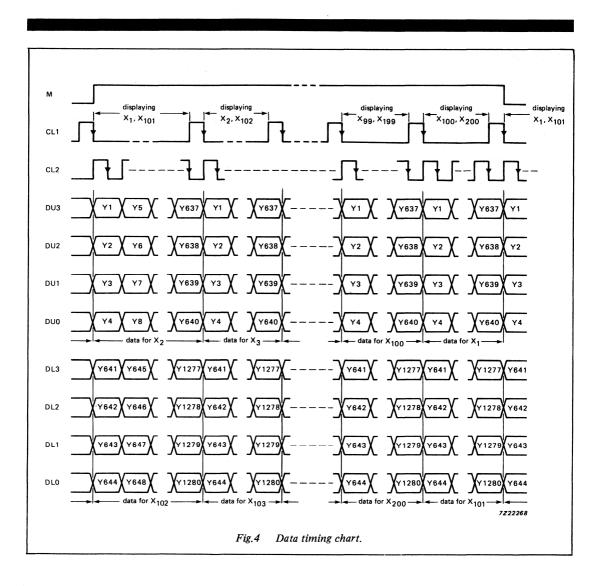

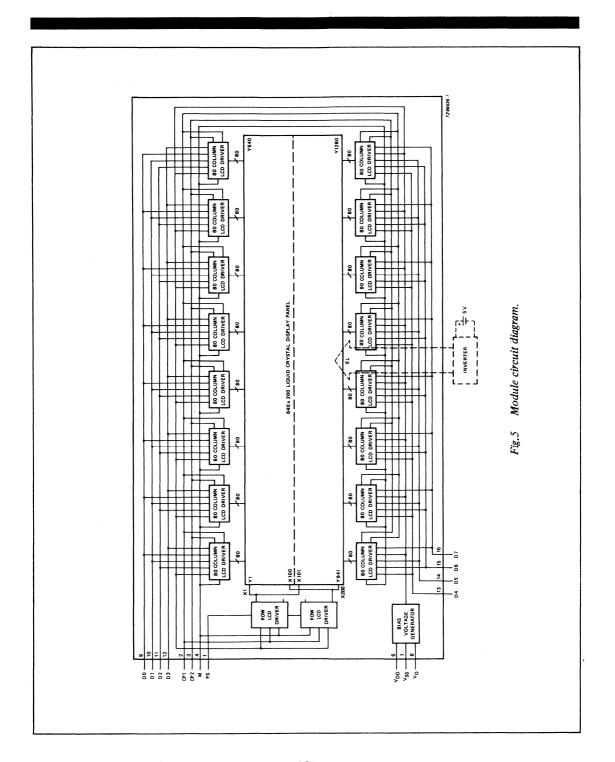

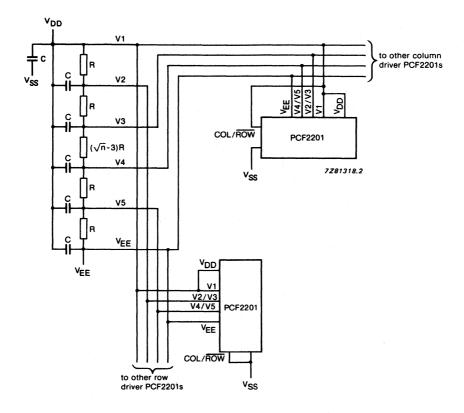

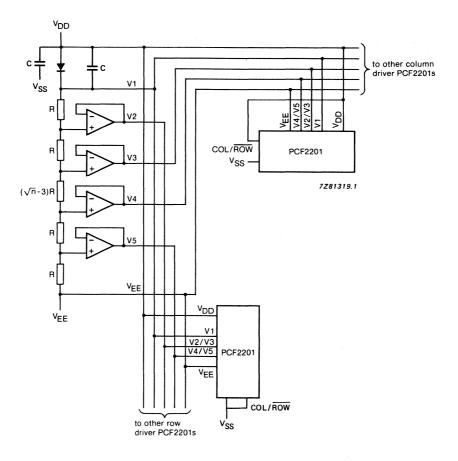

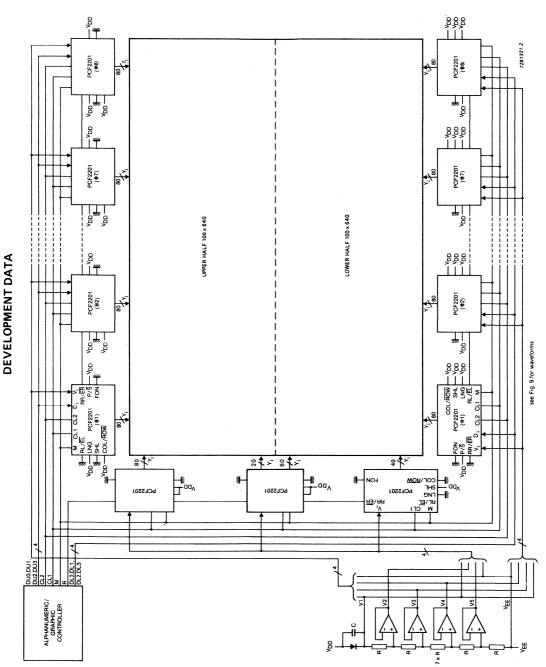

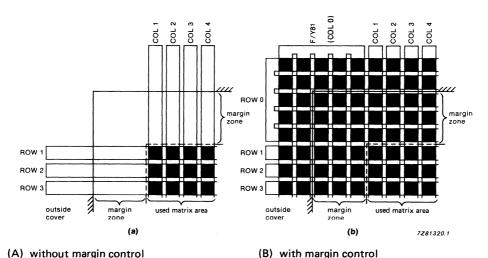

The number of horizontal (rows) and vertical (column) electrodes multiplied gives the number of pixels or dots as a pixel or dot is located at the cross point of the electrodes. The multiplex rate is determined by the number of electrodes on the short side of the display which also determines the display technology.

To enable higher contrast when using a high MUX rate display the dot areas are separated into two display parts (upper and lower). This necessitates doubling the data bits.

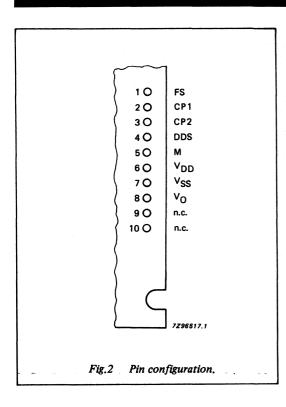

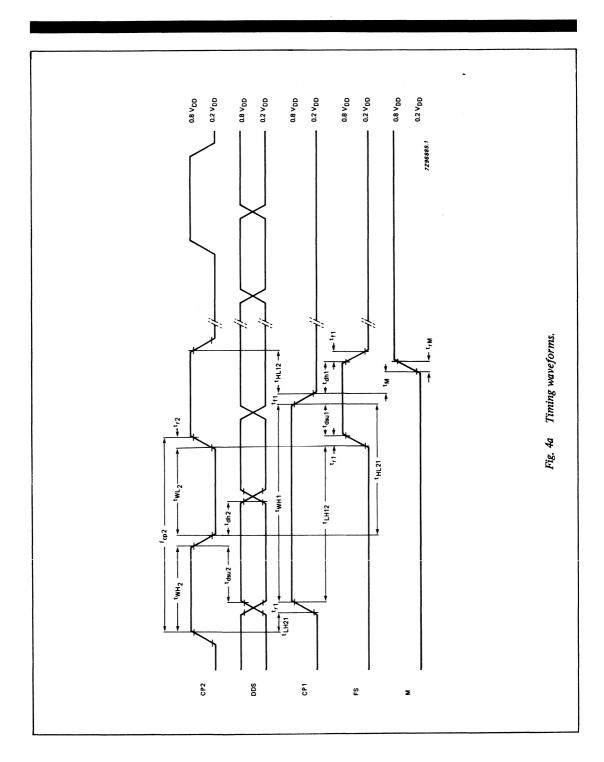

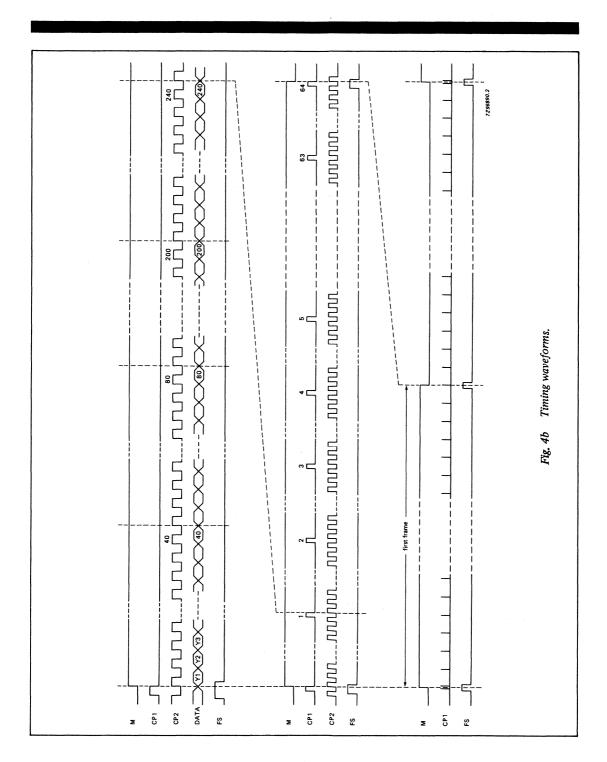

#### i) Control signals

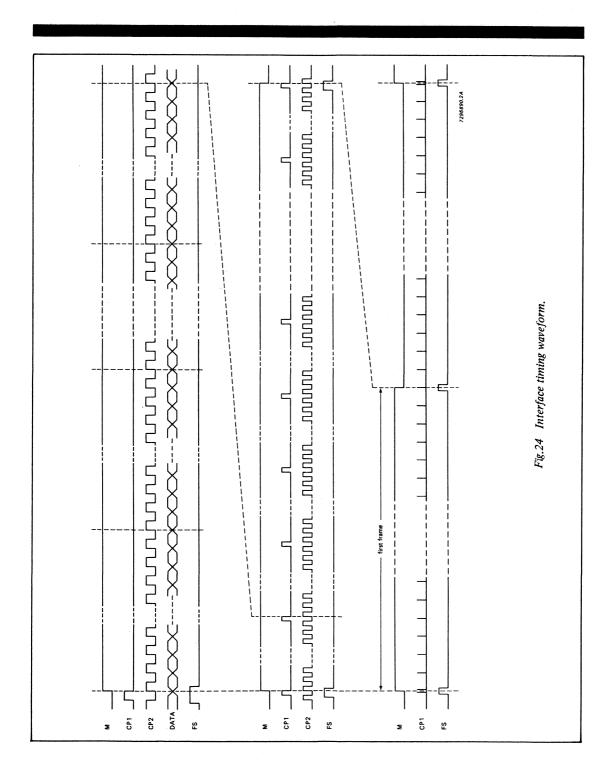

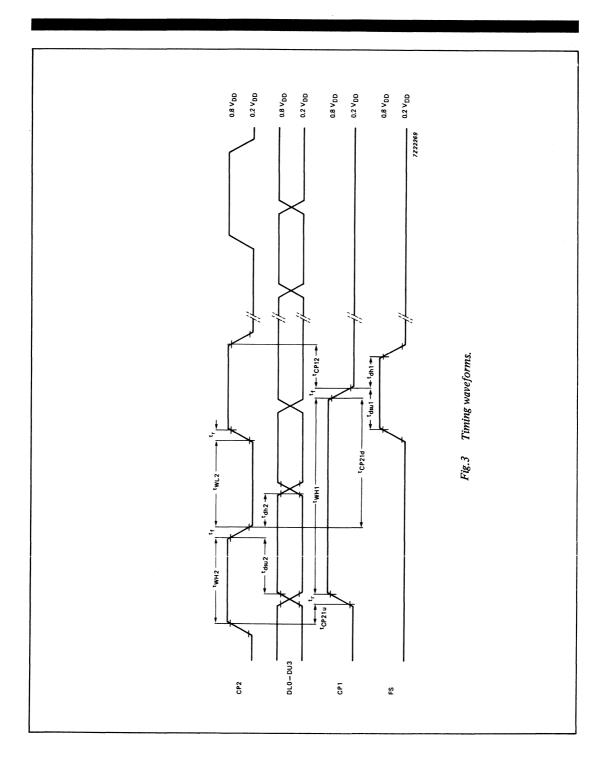

CP1 = clock pulse 1 (latch) CP2 = clock pulse 2 (shift) FS = frame synchronisation

M = signal to convert the LCD drive waveform into AC

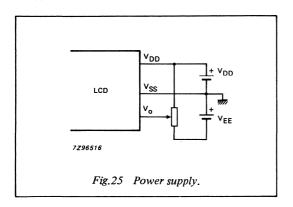

#### ii) Supply voltages

$V_{DD}$ positive supply voltage for logic  $\mathbf{v}_{SS}$ negative supply voltage for logic

(logic ground)

$v_0$ contrast adjustment voltage; operational LCD voltage;

$V_{op}$  equals  $V_{op} = V_{DD} - V_{O}$

#### iii) Data inputs

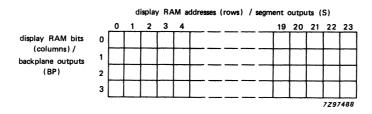

rows (Fig.23)

a) Module with 1-bit serial: used for displays with a MUX rate equal a relatively small number of dots to the number of 4-bit parallel: used for displays rows (Fig.22) with a larger number of dots b) Module with 2 X 1-bit serial: used for displays a MUX rate equal with a relatively small number to half the of dots number of 2 X 4-bit parallel: used for dis-

plays with a larger number of dots

#### Description of input data and control signals

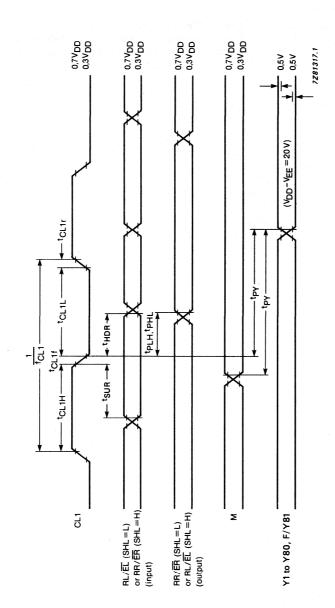

Currently we offer our dot matrix displays with 1-bit serial data input or 2 X 4-bit parallel data input.

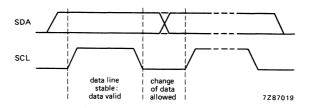

On the falling edge of CP2 the input data is sequentially transferred into the shift register in the column drivers. On the falling edge of CP1 the data is latched and displayed.

The scan sequence is started by clocking signal FS in on the HIGH to LOW transition of clock pulse CP1 after which the first row is scanning and the second row information is clocked in by CP2.

When all the data of row 2 has been entered and latched on the falling edge of CP1, the display proceeds to scanning the second row.

The data input continues until the whole area of the display is filled and then proceeds to the next display face.

# Quality

|                                  | <br>                |                         |                           |      |

|----------------------------------|---------------------|-------------------------|---------------------------|------|

|                                  | <br>                |                         |                           |      |

|                                  |                     |                         |                           | page |

|                                  |                     |                         |                           |      |

|                                  |                     |                         |                           |      |

| Quality aspects                  |                     |                         |                           | 41   |

|                                  |                     |                         |                           |      |

| Quality in design and production |                     |                         |                           |      |

| Product release                  | <br>                |                         |                           | 41   |

|                                  |                     |                         |                           |      |

| Acceptance tests                 | <br>                | , <b></b> .             |                           | 41   |

| Definition of defects            | <br>                |                         |                           | . 41 |

|                                  |                     |                         |                           |      |

| Reliability                      | <br>                |                         | <b></b>                   | 43   |

| Handling aspects                 | <br>                |                         | <b></b>                   | 43   |

|                                  |                     |                         |                           |      |

| Mounting aspects                 | <br>$\cdots \cdots$ | • • • • • • • • • • • • | · · · · · · · · · · · · · | 43   |

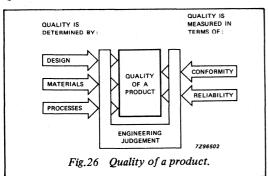

# QUALITY ASPECTS QUALITY IN DESIGN AND PRODUCTION

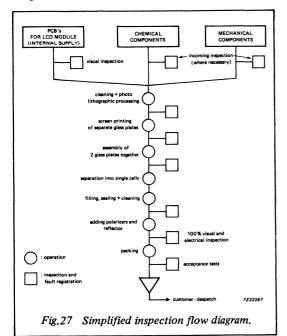

All appropriate aspects of quality are an integral part of our design rules for new LCD types, ensuring that quality is designed into our products from the beginning. The development of each new type of LCD is finalized by a product release procedure which inspects the quality of the design.

Our production quality assurance program is based upon internationally accepted standards. The results of tests carried out during incoming inspection, at the in-line inspection and final acceptance stages are used as feedback in order to continually improve our process and design rules.

#### PRODUCT RELEASE

To ensure that every LCD type fulfills its specified requirements, a product release procedure is carried out at the end of the development of each new type.

This procedure guarantees that each product withstands an extensive program of environmental tests according to IEC standards and a number of suplementary tests which are specific to LCDs.

The polarizers attached to the outside of LCDs are available in distinct quality classes so we have also classified our LCDs into:

- commercial quality grade

- extended quality grade

Consequently there are differences in the product release tests (see Table 3). The remainder of the tests are listed in Table 4.

#### ACCEPTANCE TESTS

To ensure that the devices meet the electro-optical and mechanical specifications a statistical sampling is carried out prior to delivery, as described in ISO 9001. The following AQL values apply:

for major defects: AQL 0.25

for minor defects: AQL 0.65

combined: AQL 1.0

The statistical sampling is also used to gather reliability data.

#### **DEFINITION OF DEFECTS**

#### Optical defects

Optical defects are defined as visible irregularities within the viewing area of a non-energized display. The limit of the acceptable size of an optical defect depends on the viewing distance and on the contrast of the optical fault.

The acceptance criteria for optical defects are defined by means of marginal samples, that represent esthetic borderline conditions of LCDs when mounted in the finished product.

Marginal samples for specific products can be agreed upon by the customer and us.

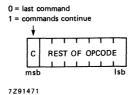

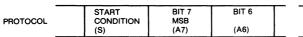

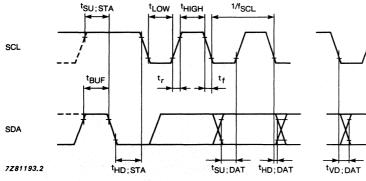

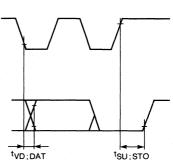

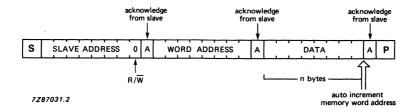

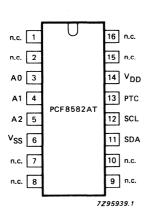

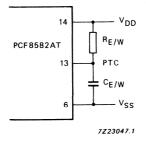

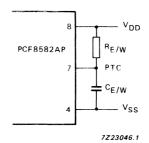

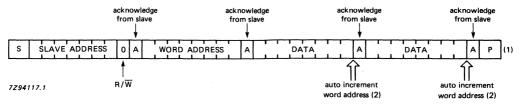

#### Electro-optical defects